# **SKP Engineering College**

Tiruvannamalai – 606611

A Course Material

on

**Digital Electronics**

By

Dr.N.Nandhagopal

**Associate Professor**

**Electronics and Communication Engineering Department**

## **Quality Certificate**

This is to Certify that the Electronic Study Material

Subject Code: EC6302

Subject Name: DIGITAL ELECTRONICS

Year/Sem:II/III

Being prepared by me and it meets the knowledge requirement of the University curriculum.

Signature of the Author Name: Dr.N.Nandhagopal Designation: Associate Professor

This is to certify that the course material being prepared by Dr.N.Nandhagopal is of the adequate quality. He has referred more than five books and one among them is from abroad author.

Signature of HD

Name:Mr.R.Saravanakumar

Seal:

Signature of the Principal Name: Dr.V.Subramania Bharathi Seal:

#### EC6302 DIGITAL ELECTRONICS

#### LTPC3003

OBJECTIVES:

- To introduce basic postulates of Boolean algebra and shows the correlation between Boolean expressions

- To introduce the methods for simplifying Boolean expressions

- To outline the formal procedures for the analysis and design of combinational circuits and sequential circuits

- To introduce the concept of memories and programmable logic devices.

- o To illustrate the concept of synchronous and asynchronous sequential circuits

#### UNIT I MINIMIZATION TECHNIQUES AND LOGIC GATES

Minimization Techniques: Boolean postulates and laws – De-Morgan's Theorem - Principle of Duality - Boolean expression - Minimization of Boolean expressions — Minterm – Maxterm - Sum of Products (SOP) – Product of Sums (POS) – Karnaugh map Minimization – Don't care conditions – Quine - Mc Cluskey method of minimization.

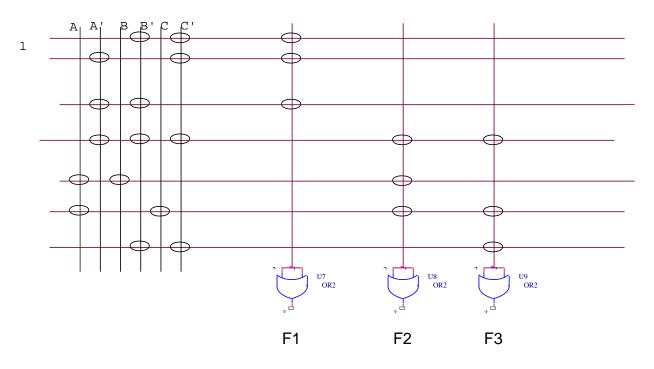

Logic Gates: AND, OR, NOT, NAND, NOR, Exclusive–OR and Exclusive–NOR Implementations of Logic Functions using gates, NAND–NOR implementations – Multi level gate implementations- Multi output gate implementations. TTL and CMOS Logic and their characteristics – Tristate gates

#### UNIT II COMBINATIONAL CIRCUITS

9

9

9

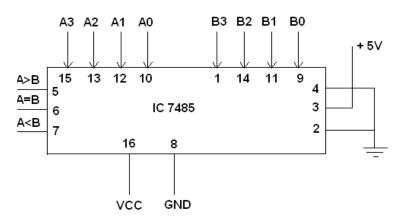

Design procedure – Half adder – Full Adder – Half subtractor – Full subtractor – Parallel binary adder, parallel binary Subtractor – Fast Adder - Carry Look Ahead adder – Serial Adder/Subtractor - BCD adder – Binary Multiplier – Binary Divider - Multiplexer/ Demultiplexer – decoder - encoder – parity checker – parity generators – code converters - Magnitude Comparator.

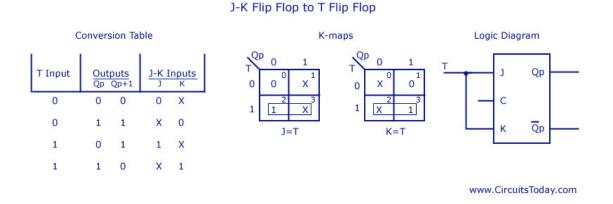

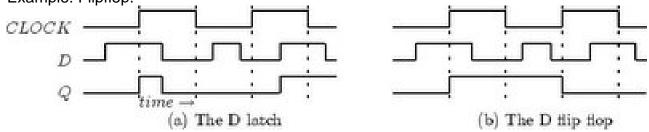

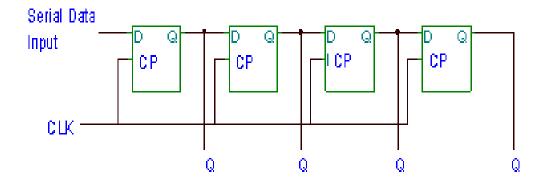

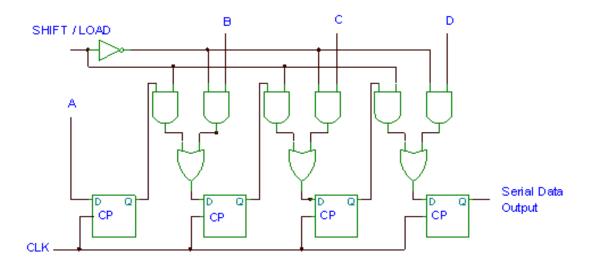

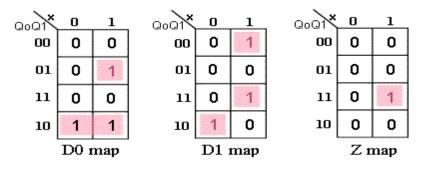

## UNIT III SEQUENTIAL CIRCUITS

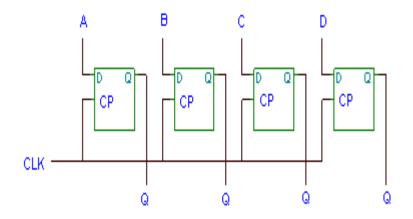

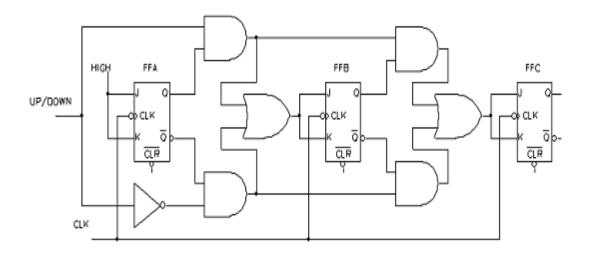

Latches, Flip-flops - SR, JK, D, T, and Master-Slave – Characteristic table and equation – Application table – Edge triggering – Level Triggering – Realization of one flip flop using other flip flops – serial adder/subtractor- Asynchronous Ripple or serial counter – Asynchronous Up/Down counter - Synchronous counters – Synchronous Up/Down counters – Programmable counters – Design of Synchronous counters: state diagram- State table – State minimization –State assignment - Excitation table and maps-Circuit implementation -Modulo–n counter, Registers – shift registers - Universal shift registers – Shift register counters – Ring counter – Shift counters - Sequence generators.

*Electronics and Communication Engineering Department* 3 *Digital Electronics*

III Sem

#### UNIT IV MEMORY DEVICES

9

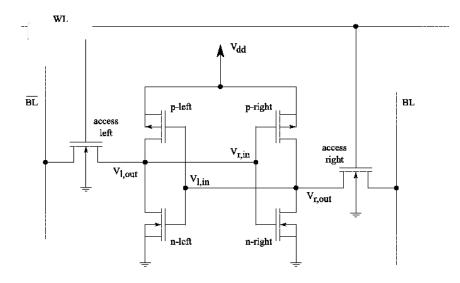

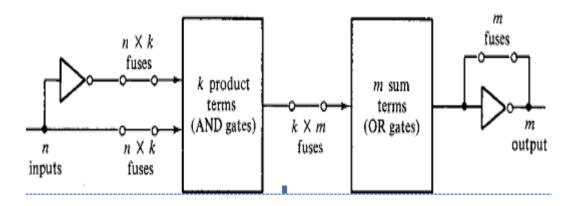

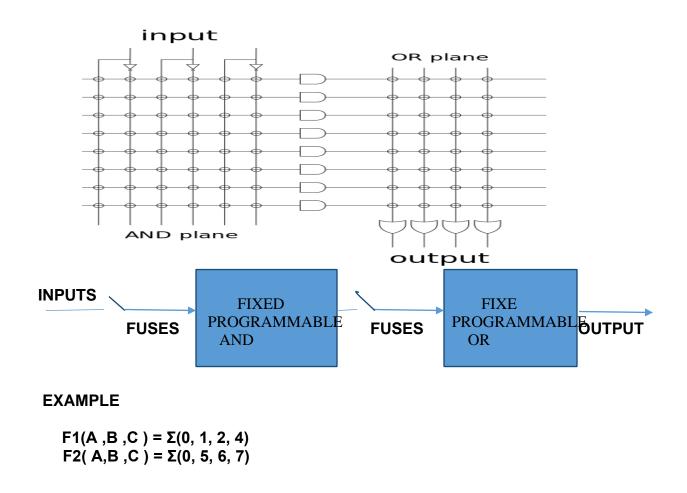

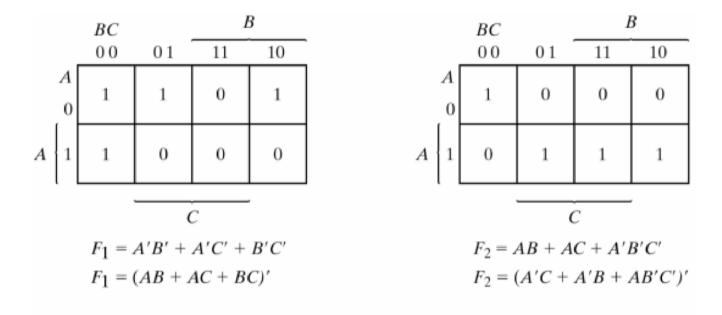

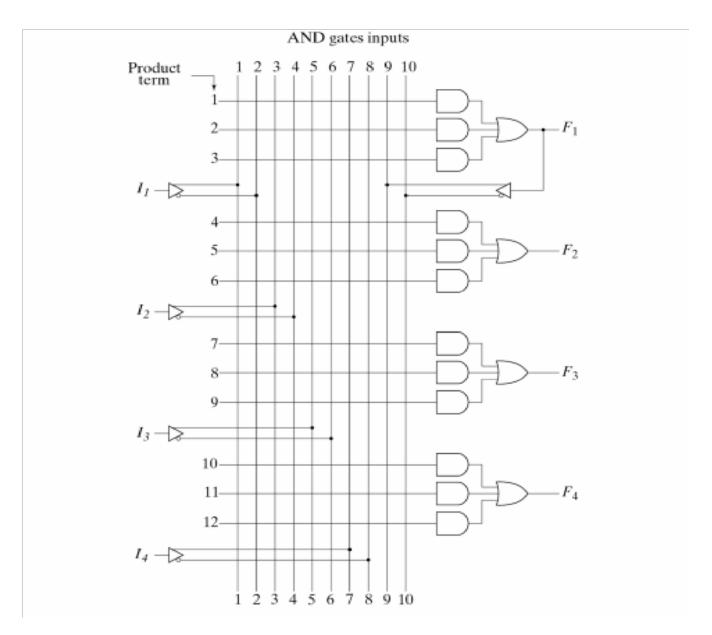

Classification of memories – ROM - ROM organization - PROM – EPROM – EPROM – EAPROM, RAM – RAM organization – Write operation – Read operation – Memory cycle -Timing wave forms – Memory decoding – memory expansion – Static RAM Cell- Bipolar RAM cell – MOSFET RAM cell – Dynamic RAM cell –Programmable Logic Devices – Programmable Logic Array (PLA) - Programmable Array Logic (PAL) – Field Programmable Gate Arrays (FPGA) - Implementation of combinational logic circuits using ROM, PLA, PAL

UNIT V SYNCHRONOUS AND ASYNCHRONOUS SEQUENTIAL CIRCUITS 9

Synchronous Sequential Circuits: General Model – Classification – Design – Use of Algorithmic State Machine – Analysis of Synchronous Sequential Circuits Asynchronous Sequential Circuits: Design of fundamental mode and pulse mode circuits – Incompletely specified State Machines – Problems in Asynchronous Circuits – Design of Hazard Free Switching circuits. Design of Combinational and Sequential circuits using VERILOG. TOTAL: 45

PERIODS OUTCOMES: Students will be able to:

- o Analyze different methods used for simplification of Boolean expressions.

- Design and implement Combinational circuits.

- Design and implement synchronous and asynchronous sequential circuits.

- Write simple HDL codes for the circuits.

TEXT BOOK:

1. M. Morris Mano, "Digital Design", 4th Edition, Prentice Hall of India Pvt. Ltd., 2008 / Pearson Education (Singapore) Pvt. Ltd., New Delhi, 2003.

## **REFERENCES**:

- 1. John F.Wakerly, "Digital Design", Fourth Edition, Pearson/PHI, 2008

- 2. John.M Yarbrough, "Digital Logic Applications and Design", Thomson Learning, 2006.

- 3. Charles H.Roth. "Fundamentals of Logic Design", 6th Edition, Thomson Learning, 2013.

- 4. Donald P.Leach and Albert Paul Malvino, "Digital Principles and Applications", 6th Edition, TMH, 2006.

- 5. Thomas L. Floyd, "Digital Fundamentals", 10th Edition, Pearson Education Inc, 2011

- 6. Donald D.Givone, "Digital Principles and Design", TMH, 2003.

# CONTENTS

| S.No | Particulars | Page |

|------|-------------|------|

| 1    | Unit – I    | 6    |

| 2    | Unit – II   | 36   |

| 3    | Unit – III  | 60   |

| 4    | Unit – IV   | 78   |

| 5    | Unit – V    | 98   |

#### Unit- I

## **Minimization Techniques and Logic Gates**

#### Part-A

# 1. State the associative property of Boolean algebra[CO1-L1]

The associative property of Boolean algebra states that the OR ing of several variables results in the same regardless of the grouping of the variables. The associative property is stated as follows:

$$A+(B+C) = (A+B) + C$$

# 2. State the commutative property of Boolean algebra[CO1-L1].

The commutative property states that the order in which the variables are OR ed makes no difference.

The commutative property is:

# 3. State the distributive property of Boolean algebra[CO1-L1].

The distributive property states that ANDing several variables and OR ing the result with a single variable is equivalent to OR ing the single variable with each of the several variables and then ANDing the sums. The distributive property is:

$$A+BC=(A+B)(A+C)$$

# 4. Simplify the following using De Morgan's theorem[CO1-L1].

[((AB)'C)'' D]' = ((AB)'C)'' + D' [(AB)' = A' + B']

$$= (A' + B') C + D'$$

*Electronics and Communication Engineering Department* 6 *Digital Electronics*

# 5. State De Morgan's theorem[CO1-L1].

De Morgan suggested two theorems that form important part of Boolean algebra.

They are,

1) The complement of a product is equal to the sum of the complements.

(AB)' = A' + B'

2) The complement of a sum term is equal to the product of the complements.

(A + B)' = A'B'

# 6. Reduce A.A'C[CO1-H1].

A.A'C = 0.C [A.A' = 1] = 0

7. Reduce A (A + B) [CO1-H1].

A

$$(A + B) = AA + AB$$

= A  $(1 + B) [1 + B = 1]$

= A.

# 8. Reduce A'B'C' + A'BC' + A'BC[CO1-H1].

$$A'B'C' + A'BC' + A'BC = A'C'(B' + B) + A'B'C$$

= A'C' + A'BC [A + A' = 1]

= A'(C' + BC)

= A'(C' + B) [A + A'B = A + B]

9. Reduce AB + (AC)' + AB'C (AB + C) [CO1-H1].

$$AB + (AC)' + AB'C (AB + C) = AB + (AC)' + AAB'BC + AB'CC$$

= AB + (AC)' + AB'CC [A.A' = 0]

= AB + (AC)' + AB'C [A.A = 1]

= AB + A' + C' = AB'C [(AB)' = A' + B']

*Electronics and Communication Engineering Department* 7 *Digital Electronics*

$$= A' + B + C' + AB'C [A + AB' = A + B]$$

= A' + B'C + B + C' [A + A'B = A + B]

= A' + B + C' + B'C

= A' + B + C' + B'

= A' + C' + 1

= 1 [A + 1 = 1]

#### 10. Simplify the following expression Y = (A + B) (A + C') (B' + C') [CO1-H1].

$$Y = (A + B) (A + C') (B' + C')$$

= (AA' + AC + A'B + BC) (B' + C') [A.A' = 0]

= (AC + A'B + BC) (B' + C')

= AB'C + ACC' + A'BB' + A'BC' + BB'C + BCC'

= AB'C + A'BC'

# 11. Show that (X + Y' + XY) (X + Y') (X'Y) = 0[CO1-H1].

$$(X + Y' + XY)(X + Y')(X'Y)$$

= (X + Y' + X) (X + Y') (X' + Y) [A + A'B = A + B]

= (X + Y') (X + Y') (X'Y) [A + A = 1]

= (X + Y') (X'Y) [A.A = 1]

= X.X' + Y'.X'.Y

= 0 [A.A' = 0]

# 12. Prove that ABC + ABC' + AB'C + A'BC = AB + AC + BC[CO1-H1].

ABC + ABC' + AB'C + A'BC=AB(C + C') + AB'C + A'BC=AB + AB'C + A'BC

Electronics and Communication Engineering Department 8 Digital Electronics

=A (B + B'C) + A'BC=A (B + C) + A'BC=AB + AC + A'BC=B (A + C) + AC=AB + BC + AC

=AB + AC +BC

13. Convert the given expression in canonical SOP form Y = AC + AB + BC [CO1-H1].

Y = AC + AB + BC= AC (B + B') + AB (C + C') + (A + A') BC

=ABC + ABC' + AB'C + AB'C' + ABC + ABC' + ABC

=ABC + ABC' + AB'C + AB'C' [A + A = 1]

# 14. Define duality property[CO1-H1].

Duality property states that every algebraic expression deducible from the postulates of Boolean algebra remains valid if the operators and identity elements are interchanged. If the dual of an algebraic expression is desired, we simply interchange OR and AND operators and replace 1's by 0's and 0's by 1's.

15. Find the complement of the functions F1 = x'yz' + x'y'z and F2 = x (y'z' + yz) [CO1-L1].

By applying De-Morgan's theorem.

$$F1' = (x'yz' + x'y'z)' = (x'yz')'(x'y'z)'$$

$$= (x + y' + z) (x + y + z')$$

$$F2' = [x (y'z' + yz)]' = x' + (y'z' + yz)'$$

$$= x' + (y'z')'(yz)'$$

Electronics and Communication Engineering Department9Digital Electronics

$$= x' + (y + z) (y' + z')$$

# 16. Define Canonical form[CO1-L1].

Boolean functions expressed as a sum of minterms ( $\sum m$ ) or product of maxterms( $\prod M$ ) are said to be in canonical form.

# 17. Define Minterm and Maxterm[CO1-L1]..

Each individual term in standard SOP form is called a Minterm

Example: f(A, B, C) = AB'C + ABC + A'BC'

Each individual term in standard POS form is called a Maxterm

Example: f(A, B, C) = (A+B+C)(A+B'+C)

# 18. What are the methods adopted to reduce Boolean function? [CO1-L1].

- i) Karnaugh map

- ii) Tabular method or Quine Mc-Cluskey method

- iii) Variable entered map technique.

# 19. State the limitations (or) disadvantages of karnaugh map. [CO1-L1].

i) Generally it is limited to six variable map (i.e.) more then six variable involving expressions are not reduced.

ii) The map method is restricted in its capability since they are useful for simplifying only Boolean expression represented in standard form.

# 20. What is a karnaugh map? [CO1-L1].

A karnaugh map or k map is a pictorial form of truth table, in which the map diagram is made up of squares, with each squares representing one minterm of the function.

# 21. Find the minterms of the logical expression Y = A'B'C' + A'B'C + A'BC + ABC'[CO1-H1].

Y = A'B'C' + A'B'C + A'BC + ABC'=m0 + m1 +m3 +m6

=∑ m (0, 1, 3, 6)

# 22. Write the maxterms corresponding to the logical expression[CO1-L1].

$$Y = (A + B + C') (A + B' + C') (A' + B' + C)$$

= (A + B + C') (A + B' + C') (A' + B' + C)

=M1.M3.M6

=  $\prod M (1, 3, 6)$

# 23. What are called don't care conditions? [CO1-L1].

In some logic circuits certain input conditions never occur, therefore the corresponding output never appears. In such cases the output level is not defined, it can be either high or low. These output levels are indicated by 'X' or'd' in the truth tables and are called don't care conditions or incompletely specified functions.

# 24. What is a prime implicant? [CO1-L1].

A prime implicant is a product term obtained by combining the maximum possible number of adjacent squares in the map.

# 25. What is an essential implicant? [CO1-L1].

If a min term is covered by only one prime implicant, the prime implicant is said to be essential

# 26. What is a Logic gate? [CO1-L1].

Logic gates are the basic elements that make up a digital system. The electronic gate is a circuit that is able to operate on a number of binary inputs in order to perform a particular logical function.

# 27. Which gates are called as the universal gates? What are its advantages?(Nov/Dec 2009) [CO1-L1].

The NAND and NOR gates are called as the universal gates. These gates are used to perform any type of logic application.

# 28. Classify the logic family by operation? [CO1-L1].

The Bipolar logic family is classified into Saturated logic and Unsaturated logic.

- ✓ The RTL, DTL, TTL, I2L, HTL logic comes under the saturated logic family.

- $\checkmark$  The Schottky TTL, and ECL logic comes under the unsaturated logic family.

# 29. Mention the classification of saturated bipolar logic families. [CO1-L1].

The bipolar logic family is classified as follows:

**RTL- Resistor Transistor Logic**

DTL- Diode Transistor logic

**IIL- Integrated Injection Logic**

TTL- Transistor Transistor Logic

ECL- Emitter Coupled Logic

# 30. Define Fan-out? [CO1-L1].

Fan out specifies the number of standard loads that the output of the gate can drive without impairment of its normal operation.

# 31. Define power dissipation? [CO1-L1].

Power dissipation is measure of power consumed by the gate when fully driven by all its inputs.

# 32. What is propagation delay? [CO1-L1].

Propagation delay is the average transition delay time for the signal to propagate from input to output when the signals change in value. It is expressed in ns.

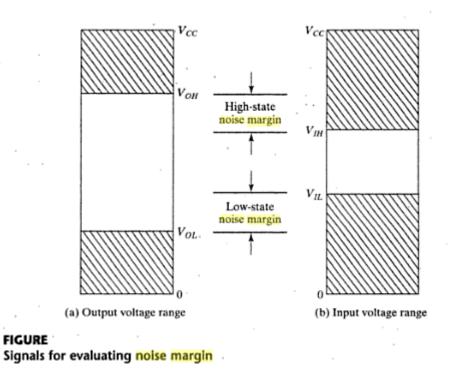

# 33. Define noise margin? [CO1-L1].

It is the maximum noise voltage added to an input signal of a digital circuit that does not cause an undesirable change in the circuit output. It is expressed in volts.

# 34. What are the types of TTL logic? [CO1-L1].

- 1. Open collector output

- 2. Totem-Pole Output

- 3. Tri-state output.

# 35. What is depletion mode operation MOS? [CO1-L1].

If the channel is initially doped lightly with p-type impurity a conducting channel exists at zero gate voltage and the device is said to operate in depletion mode.

# 36. What is enhancement mode operation of MOS?

If the region beneath the gate is left initially uncharged the gate field must induce a channel before current can flow. Thus the gate voltage enhances the channel current and such a device is said to operate in the enhancement mode.

# 37. Mention the characteristics of MOS transistor? [CO1-L1].

1. The n- channel MOS conducts when its gate- to- source voltage is positive.

- 2. The p- channel MOS conducts when its gate- to- source voltage is negative

- 3. Either type of device is turned off if its gate- to- source voltage is zero.

Electronics and Communication Engineering Department 13 Digital Electronics

# 38. How schottky transistors are formed and state its use? [CO1-L1].

A schottky diode is formed by the combination of metal and semiconductor. The presence of schottky diode between the base and the collector prevents the transistor from going into saturation. The resulting transistor is called as schottky transistor. The use of schottky transistor in TTL decreases the propagation delay without a sacrifice of power dissipation.

# 39. State advantages and disadvantages of TTL[CO1-L1].

Advantages:

Easily compatible with other ICs

Low output impedance

Disadvantages:

Wired output capability is possible only with tristate and open collector types Special circuits in Circuit layout and system design are required.

**40. When does the noise margin allow digital circuits to function properly? [CO1-L1].** When noise voltages are within the limits of VNA (High State Noise Margin) and VNK for a particular logic family.

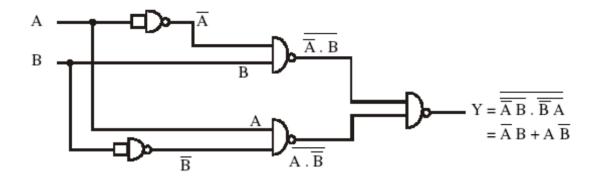

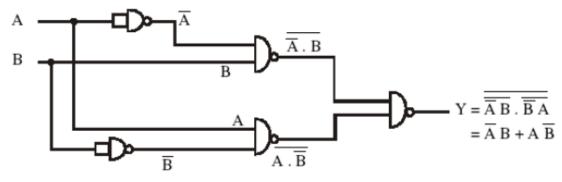

41. Implement the Boolean Expression for EX – OR gate using NAND Gates.[CO1-L1].

# 42. Define Binary Logic[CO1-L1].

Binary logic consists of binary variables and logical operations. The variables are

*Electronics and Communication Engineering Department* 14 *Digital Electronics*

designated by the alphabets such as A, B, C, x, y, z, etc., with each variable having only two distinct values: 1 and 0. There are three basic logic operations: AND, OR, and NOT.

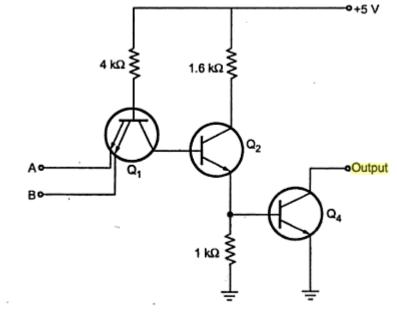

# 43. What is Totem output? [CO1-L1].

In two input NAND gate the transistors  $Q_3 \& Q_4$  form a totem pole output. The active pull up formed by  $Q_3 \& Q_4$  has specific advantage. Totem pole transistors are used because they produce a low output impedance.

# 44. State the different classification of binary codes? [CO1-L1].

- 1. Weighted codes

- 2. Non weighted codes

- 3. Reflective codes

- 4. Sequential codes

- 5. Alphanumeric codes

- 6. Error Detecting and correcting codes.

## Part-B

# 1. Explain SOP AND POS FORMS. [CO1-L2].

# Sum of Products (SOP):

The logical sum of two or more logical product terms is called a Sum of Products expression. It is basically an OR operation of AND operated variables. Example: AB + ABC + CDE.

# Product of Sum (POS):

A product of sums expression is a logical product of two or more logical sum terms. It is basically an AND operation of OR operated variables.

Example : (A+B) \* (A + B + C) \* (C + D).

The term "standard" here means that the expression consists exclusively of **minterms** (in the case of Standard SOP) or **maxterms** (in the case of Standard POS).

*Electronics and Communication Engineering Department* 15 *Digital Electronics*

#### Converting Boolean Expressions into SOP/POS Form:

The process of converting any Boolean expression into either POS or SOP form (canonical or otherwise) is very straightforward.

To get the expression in SOP form, you simply distribute all AND operations over any OR operations and continue doing this as long as possible. When finished, you will have an expression in SOP form. If you want it in canonical form, then you simply expand each term as necessary.

To get the expression in POS form, you simply distribute all OR operations over any AND operations and continue doing this as long as possible. When finished, you will have an expression in POS form. If you want it in canonical form, then you simply expand each term as necessary.

## 2. What are Minterms and Maxterms? [CO1-L1].

Each individual term in standard SOP form is called minterm. Minterms are standard product.(AND terms)

Each individual term in standard POS form is called maxterm. Maxterms are standard sum.(OR terms)

| Va | ariable |   | М      | Minterm        |          | axterm         |

|----|---------|---|--------|----------------|----------|----------------|

| х  | у       | Ζ | Term   | Designation    | Term     | Designation    |

| 0  | 0       | 0 | x'y'z' | m <sub>0</sub> | x+y+z    | M <sub>0</sub> |

| 0  | 0       | 1 | x'y'z  | m <sub>1</sub> | x+y+z'   | M <sub>1</sub> |

| 0  | 1       | 0 | x'yz'  | m <sub>2</sub> | x+y'+z   | M <sub>2</sub> |

| 0  | 1       | 1 | x'yz   | m <sub>3</sub> | x+y'+z'  | M <sub>3</sub> |

| 1  | 0       | 0 | xy'z'  | m <sub>4</sub> | x'+y+z   | M <sub>4</sub> |

| 1  | 0       | 1 | xy'z   | m <sub>5</sub> | x'+y+z'  | M <sub>5</sub> |

| 1  | 1       | 0 | xyz'   | m <sub>6</sub> | x'+y'+z  | M <sub>6</sub> |

| 1  | 1       | 1 | xyz    | m <sub>7</sub> | x'+y'+z' | M <sub>7</sub> |

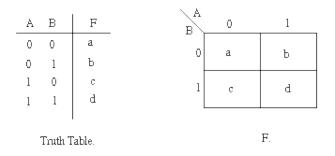

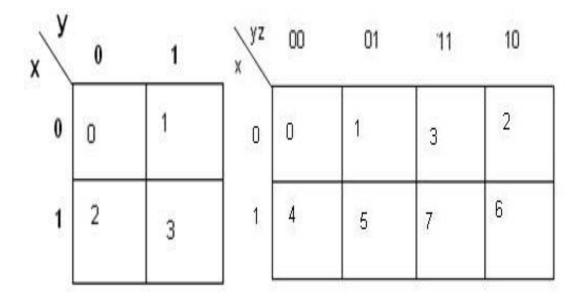

## 3. Write short notes on various K-MAP representations [CO1-L1].

A Karnaugh map provides a pictorial method of grouping together expressions with common factors and therefore eliminating unwanted variables. The Karnaugh map can also be described as a special arrangement of a truth table.

The diagram below illustrates the correspondence between the Karnaugh map and the truth table for the general case of a two variable problem.

The values inside the squares are copied from the output column of the truth table, therefore there is one square in the map for every row in the truth table. Around the edge of the Karnaugh map are the values of the two input variable. A is along the top and B is down the left hand side. The diagram below explains this:

The values around the edge of the map can be thought of as coordinates. So as an example, the square on the top right hand corner of the map in the above diagram has coordinates A=1 and B=0. This square corresponds to the row in the truth table where A=1 and B=0 and F=1. Note that the value in the F column represents a particular function to which the Karnaugh map corresponds.

Electronics and Communication Engineering Department 17 Digital Electronics

#### III Sem

If we have n variables then there would be 2<sup>n</sup> min terms and hence 2<sup>n</sup> number of blocks in the K-map and also min terms are arranged in their gray code order (not in binary order). 2-variable map and 3-variable map are shown below:

Also there are minterms mentioned in the squares of the map

Similarly we can have a K-map for 4 variables, 5 variables, 6 variables etc but we generally use only till 4 variables maps as higher maps are difficult to use.

Now to simplify any expression we first convert the expression into its canonical form and then mark a 1 in the corresponding column of min terms present in the expression and then we'll combine 1's and make groups of 2 or 4 or 8 or 16 terms and then write the shortened expression.

Any two adjacent squares in the K map differ only by 1 bit change. So the thing where the term corresponding to one square differs from the term corresponding to the adjacent square is that one literal is in compliment form and same literal in other is non-compliment. So sum of those min terms would lead to elimination of one literal and simplified result would be a single AND term.

Electronics and Communication Engineering Department 18 Digital Electronics

Also note that squares on one edge of the k-map are adjacent to the opposite edge of the Kmap. Hence m0 is adjacent to m2, m4 is adjacent to m6 but m0 is not adjacent to m6. Similarly we can check the adjacent cells in 4-variable map.

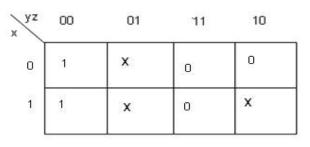

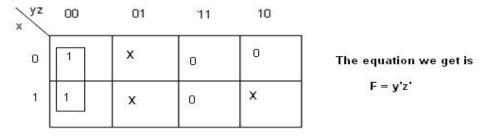

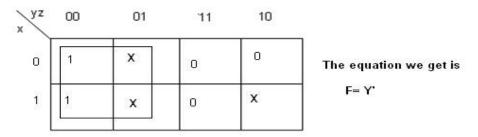

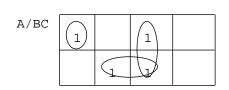

## 4. Explain Don't care conditions[CO1-L2].

When ever there are don't cares present in the K-map then we have the option of including don't care in the group to maximize the size of group and hence we get more minimized form but this is not compulsory to include each and every don't care. So we can use don't care to our advantage otherwise skip them.

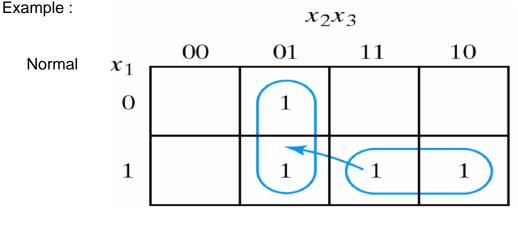

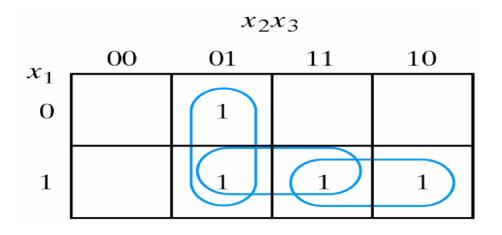

e.g. Minimize the K-map given below:

If we ignore don't care then we make groups of 1 then we get the equations as

But if we use the don't cares then we make groups as

*Electronics and Communication Engineering Department* 19 *Digital Electronics*

And we see that we have used 2 don't care and we make a group of 4 rather than 2 while we skip the 3<sup>rd</sup> don't care as we do not have to use each don't care. Hence we see that using 2 out of 3 don't care we have got more minimized equation.

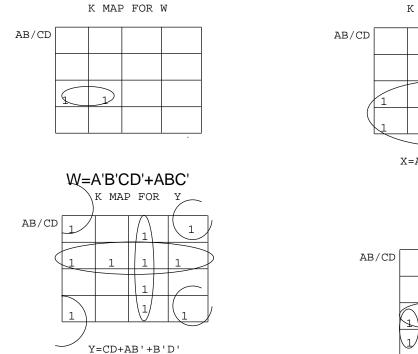

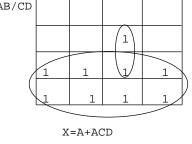

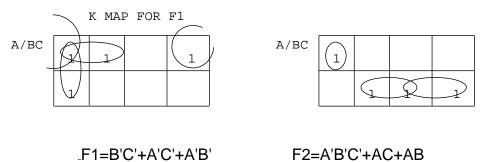

## 5. Simplify the given functions using K- Map Minimization method.

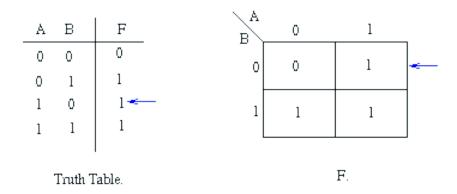

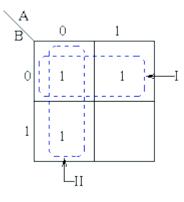

# (1) Simplify $Z = f(A,B) = \overline{A}\overline{B} + A \overline{B} + \overline{A}B[CO1-H1]$ .

Consider the expression  $Z = f(A,B) = \overline{AB} + A \overline{B} + \overline{AB}$  plotted on the Karnaugh map:

Pairs of 1's are *grouped* as shown above, and the simplified answer is obtained by using the following steps:

Note that two groups can be formed for the example given above, bearing in mind that the largest rectangular clusters that can be made consist of two 1s. Notice that a 1 can belong to more than one group.

The first group labelled I, consists of two 1s which correspond to A = 0, B = 0 and A = 1, B = 0. Put in another way, all squares in this example that correspond to the area of the map where B = 0 contains 1s, independent of the value of A. So when B = 0 the output is 1. The expression of the output will contain the term  $\overline{B}$

For group labelled II corresponds to the area of the map where A = 0. The group can therefore be defined as  $\overline{A}$ . This implies that when A = 0 the output is 1. The output is therefore1wheneverB=0andA=0 Hence the simplified answer is Z =  $\overline{A}$  +  $\overline{B}$

Electronics and Communication Engineering Department 20 Digital Electronics

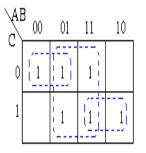

# 6.. Minimize the following problems using the Karnaugh maps method[CO1-H1].

$$Z = f(A,B,C) = \overline{A}\overline{B}\overline{C} + \overline{A}B + AB\overline{C} + AC$$

$$Z = f(A,B,C) = \overline{A}B + B\overline{C} + BC + A\overline{B}\overline{C}$$

1.

$$Z = f(A,B,C) = \overline{A}\overline{B}\overline{C} + \overline{A}B + AB\overline{C} + AC$$

By using the <u>rules</u> of simplification and ringing of <u>adjacent</u> cells in order to make as many variables redundant, the minimised result obtained is  $B + AC + \overline{AC}$ 2.  $Z = f(A,B,C) = \overline{A}B + B\overline{C} + BC + A\overline{BC}$

By using the rules of simplification and ringing of adjacent cells in order to make as many variables redundant, the minimised result obtained is B + A c

#### 7. Explain redundancy in K map. [CO1-L2].

#### Redundant groups

A groups of 1s or 0s whose all members are overlapped by other groups is called redundant group. We don't consider this group while writing the simplified equations from the K-map.

| , zw<br>xy | 00 | 01 | 11 | 10 |

|------------|----|----|----|----|

| 00         | 0  | 1  | 0  | 0  |

| 01         | Ŕ  | Þ  | 0  | 0  |

| 11         | 1  | o  | o  | o  |

| 10         | 0  | 0  | 0  | Ō  |

In the above K-map the group which is represented by the oval is a redundant group and hence while writing the equations we ignore it or we don't make this kind of group and the K-map representation becomes as given next:

The equation we get is

F = yz'w' + x'z'w (ignoring the redundant group)

If we consider this group then equation would be F = yz'w' + x'z'w + x'yz'

And this is a not the simplified expression and hence WRONG.

K-map without the redundant group is:

| xy<br>xy | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 00       | 0  | 1  | o  | o  |

| 01       | 1  | 1  | O  | 0  |

| 11       | 1  | 0  | 0  | 0  |

| 10       | 0  | 0  | O  | 0  |

# 8.Simplify the function using Karnaugh map[CO1-H1].

- (i) F (ABCD) =  $\sum (0, 1, 2, 4, 5, 7, 11, 15)$ (ii) F (WXYZ) =  $\sum (2, 3, 10, 11, 12, 13, 14, 15)$

(i) F(A,B,C,D) = ∑ (0,1,2,4,5,7,11,15)

| 1 | 1 |   | 1 |

|---|---|---|---|

| 1 | 1 | 1 |   |

|   |   | 1 |   |

|   |   | 1 |   |

$= \overline{ABD} + \overline{AC} + BCD + ACD$

(ii)  $F(W,X,Y,Z) = \sum (2,3,10,11,12,13,14,15)$

|  | 1 | 1 |

|--|---|---|

|  |   |   |

**Digital Electronics**

| 1 1 | 1 | 1 | 1 | 1 |

|-----|---|---|---|---|

|     |   |   | 1 | 1 |

= x'y=wx

9.(i) Express the function  $f(x,y,z) = XY + X\overline{Z}$  as a product of sum terms form.

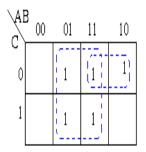

(ii) Express the following function as the minimal sum of products, using a K-map F (a,b,c,d) = $\sum m(0,2,4,5,6,8,10,15) + \sum \Phi(7,13,14)$  [CO1-H1].

Solution:

(i)

$$f(x,y,z) = XY + X\overline{Z}$$

$$= X(Y + \overline{Z})$$

$$= (X + Y \bullet \overline{Y} + Z \bullet \overline{Z})(X \bullet \overline{X} + Y + \overline{Z})$$

$$= \frac{(X + Y + Z)(X + Y + \overline{Z})(X + \overline{Y} + Z)(X + \overline{Y} + \overline{Z})(X + Y + \overline{Z})}{(\overline{X} + Y + \overline{Z})}$$

$$= (X + Y + Z)(X + Y + \overline{Z})(X + \overline{Y} + Z)(X + \overline{Y} + \overline{Z})(\overline{X} + Y + \overline{Z})$$

$$= M_0 \qquad M_1 \qquad M_2 \qquad M_3 \qquad M_5$$

$$= \pi M (0, 1, 2, 3, 5)$$

(ii) F (a,b,c,d) =  $\sum m(0,2,4,5,6,8,10,15) + \sum \Phi(7,13,14)$

| 1 |   |   | 1 |

|---|---|---|---|

| 1 | 1 | х | 1 |

|   | х | 1 | x |

| 1 |   |   | 1 |

$$= \overline{bd} + \overline{ab} + bcd$$

*Electronics and Communication Engineering Department* 24 *Digital Electronics*

10.Simplify the Boolean function using K-map and tabular methods. Compare the methods. F (A, B, C, D) =  $\sum m(4,5,6,7,8) d (A, B, C, D) = \sum m(11,12,13,14,15)$  Implement using only NAND gates[CO1-H1].

Solution:

## Tabulation method:

(i) Arranging the minterms according to the number of 1's

| Minterm         | <b>Binary Representation</b> | Minterm         | <b>Binary Representation</b> |

|-----------------|------------------------------|-----------------|------------------------------|

| m <sub>4</sub>  | 0100                         | $m_4$           | 0100                         |

| m <sub>5</sub>  | 0101                         | m <sub>8</sub>  | 1000                         |

| m <sub>6</sub>  | 0110                         | m₅              | 0101                         |

| m <sub>7</sub>  | 0111                         | $m_6$           | 0110                         |

| m <sub>8</sub>  | 1000                         | $m_{12}$        | 1100                         |

| m <sub>11</sub> | 1011                         | m <sub>7</sub>  | 0111                         |

| m <sub>12</sub> | 1100                         | $m_{11}$        | 1011                         |

| m <sub>13</sub> | 1101                         | <b>m</b> 13     | 1101                         |

| m <sub>14</sub> | 1110                         | $m_{14}$        | 1110                         |

| m <sub>15</sub> | 1111                         | m <sub>15</sub> | 1111                         |

Elimination of literals:

| Minterm | <b>Binary Representation</b> | Minterm   | <b>Binary Representation</b> |

|---------|------------------------------|-----------|------------------------------|

| 4,5     | 010-                         | 4,5,6,7   | 01                           |

| 4,6     | 01-0                         | 4,6,5,7   | 01                           |

| 4,12    | -100                         | 4,12,5,13 | -10-                         |

| 8,12    | 1-00                         | 5,7,13,15 | -1-1                         |

| 5,7     | 01-1                         | 5,13,7,15 | -1-1                         |

| 5,13    | -101                         | 6,7,14,15 | -11-                         |

| 6,7     | 011-                         | 6,14,7,15 | -11-                         |

*Electronics and Communication Engineering Department* 25 *Digital Electronics*

| 6,14                            | -110 |  |

|---------------------------------|------|--|

| 7,15                            | -111 |  |

| 11,15                           | 1-11 |  |

| 13,15                           | 11-1 |  |

| 7,15<br>11,15<br>13,15<br>14,15 | 111- |  |

Further elimination of literals:

| Minterm             | <b>Binary Representation</b> |

|---------------------|------------------------------|

| 4,5,6,7             | 01                           |

| 5,7,13,15           | -1-1                         |

| 4,5,12,13,6,7,14,15 | -1                           |

| 8,12                | 1-00                         |

| 11,15               | 1-11                         |

Selecting the minimum number of prime implicants as

| Prime Implicants    | $m_4$ | $m_5$ | m <sub>6</sub> | m <sub>7</sub> | m <sub>8</sub> | m <sub>11</sub> | <b>m</b> <sub>12</sub> | m <sub>13</sub> | m <sub>14</sub> | m <sub>15</sub> |

|---------------------|-------|-------|----------------|----------------|----------------|-----------------|------------------------|-----------------|-----------------|-----------------|

| 4,5,6,7             | *     | *     | *              | *              |                |                 |                        |                 |                 |                 |

| 5,7,13,15           |       | *     |                | *              |                |                 |                        | *               |                 | *               |

| 4,5,12,13,6,7,14,15 | *     | *     | *              | *              |                |                 | *                      | *               | *               | *               |

| 8,12                |       |       |                |                | *              |                 | *                      |                 |                 |                 |

| 11,15               |       |       |                |                |                | *               |                        |                 |                 | *               |

$$= B + A\overline{C}\overline{D}$$

## 11. State and prove demorgan's theorem and expand the function[CO1-H1].

$\mathbf{F} = (((A+B)C + \overline{C}D))$

Solution:

# 12. Explain the characteristics of CMOS logic[CO1-L2].

*Electronics and Communication Engineering Department* 26 *Digital Electronics*

- Dissipates low power: The power dissipation is dependent on the power supply voltage, frequency, output load, and input rise time. At 1 MHz and 50 pF load, the power dissipation is typically 10 nW per gate.

- Short propagation delays: Depending on the power supply, the propagation delays are usually around 25 nS to 50 nS.

- Rise and fall times are controlled: The rise and falls are usually ramps instead of step functions, and they are 20 40% longer than the propagation delays.

- Noise immunity approaches 50% or 45% of the full logic swing.

- Levels of the logic signal will be essentially equal to the power supplied since the input impedance is so high.

- Voltage levels range from 0 to VDD where VDD is the supply voltage. A low level is anywhere between 0 and 1/3 VDD while a high level is between 2/3 VDD and VDD.

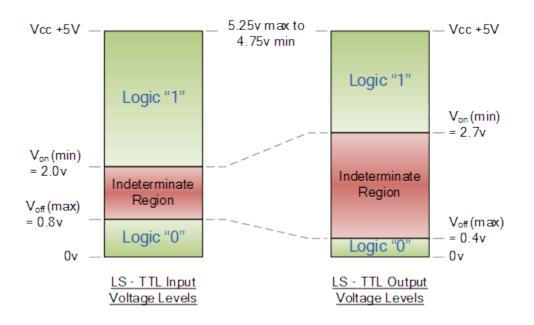

# Characteristics of TTL logic:

- Power dissipation is usually 10 mW per gate.

- Propagation delays are 10 nS when driving a 15 pF/400 ohm load.

- Voltage levels range from 0 to Vcc where Vcc is typically 4.75V 5.25V. Voltage range 0V 0.8V creates logic level 0. Voltage range 2V Vcc creates logic level 1.

# CMOS compared to TTL:

- CMOS components are typically more expensive than TTL equivalents. However, CMOS technology is usually less expensive on a system level due to CMOS chips being smaller and requiring less regulation.

- CMOS circuits do not draw as much power as TTL circuits while at rest. However, CMOS power consumption increases faster with higher clock speeds than TTL does.

Lower current draw requires less power supply distribution, therefore causing a simpler and cheaper design.

- Due to longer rise and fall times, the transmission of digital signals becomes simpler and less expensive with CMOS chips.

- CMOS components are more susceptible to damage from electrostatic discharge than TTL components.

Electronics and Communication Engineering Department 27 Digital Electronics

# 13. Explain the characteristics of digital logic families[CO1-L2].

#### Fan-in

The fan-in of a gate is the number of inputs connected to the gate without any degradation in the voltage levels. For example, an eight-input gate requires one Unit Load(UL) per input. Its fan-in is 8. This parameter determines the functional capabilities of a logic circuit.

#### Fan-out :

Fan-out is the maximum number of similar logic gates that a gate can drive without any degradation in voltage levels. The fan-out of a gate specifies the number of standard loads that can be connected to the output of the gate without degrading its normal operation. A standard load is usually defined as the amount of current needed by an input of another gate in the same logic family. Fan-out is calculated from the amount of current available in the output of a gate and the amount of current needed in each input of a gate.

#### Totem output

In TTL gate, the transistor Q4 'sits' upon Q3. Such a configuration is called totem pole and it has low output impedance. Hence output voltage can change quickly from one state of the other due to rapidly charging of stray capacitance. So propogation delay is low in totem-output.

## Noise Margin:

Noise is a term used to denote an undesirable signal that is superimposed upon the normal operating signal. The noise margin is the maximum noise voltage added to an input signal of a digital circuit that does not cause an undesirable change in the circuit's output. Noise margin is expressed in volts and represents the maximum noise signal that can be tolerated by the gate.

14.Explain the operation of a two input NAND gate with Open collector output TTL NAND[CO1-L2].

Fig. Open Collector 2 input TTL NAND gate

*Electronics and Communication Engineering Department* 29 *Digital Electronics*

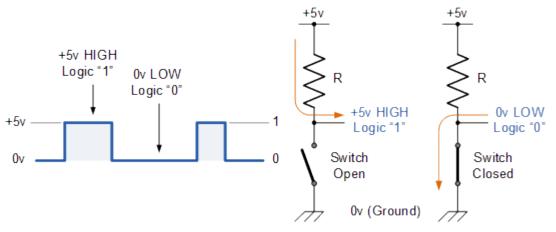

## 15. Write short notes onDigital Logic States[CO1-L1].

The Digital Logic Gate is the basic building block from which all digital electronic circuits and microprocessor based systems are constructed from. Basic digital logic gates perform logical operations of AND, OR and NOT on binary numbers.

In digital logic design only two voltage levels or states are allowed and these states are generally referred to as Logic "1" and Logic "0", High and Low, or True and False. These two states are represented in *Boolean Algebra* and standard truth tables by the binary digits of "1" and "0" respectively. A good example of a digital signal is a simple light as it is either "ON" or "OFF" but not both at the same time.

Most *digital logic gates* and logic systems use "Positive logic", in which a logic level "0" or "LOW" is represented by a zero voltage, 0v or ground and a logic level "1" or "HIGH" is represented by a higher voltage such as +5 volts, with the switching from one voltage level to the other, from either a logic level "0" to a "1" or a "1" to a "0" being made as quickly as possible to prevent any faulty operation of the logic circuit.

There also exists a complementary "Negative Logic" system in which the values and the rules of a logic "0" and a logic "1" are reversed but in this tutorial section about digital logic gates we shall only refer to the positive logic convention as it is the most commonly used.

# 16. Explain TTL logic circuit and its Input & Output Voltage Levels. [CO1-L1Nov 2014]

In standard TTL (transistor-transistor logic) IC's there is a pre-defined voltage range for the input and output voltage levels which define exactly what is a logic "1" level and what is a logic "0" level and these are shown below.

There are a large variety of logic gate types in both the bipolar 7400 and the CMOS 4000 families of digital logic gates such as 74Lxx, 74LSxx, 74ALSxx, 74HCxx, 74HCTxx, 74ACTxx etc, with each one having its own distinct advantages and disadvantages compared to the other. The exact switching voltage required to produce either a logic "0" or a logic "1" depends upon the specific logic group or family.

However, when using a standard +5 volt supply any TTL voltage input between 2.0v and 5v is considered to be a logic "1" or "HIGH" while any voltage input below 0.8v is recognised as a logic "0" or "LOW". The voltage region in between these two voltage levels either as an input or as an output is called the *Indeterminate Region* and operating within this region may cause the logic gate to produce a false output.

The CMOS 4000 logic family uses different levels of voltages compared to the TTL types as they are designed using field effect transistors, or FET's. In CMOS technology a logic "1" level operates between 3.0 and 18 volts and a logic "0" level is below 1.5 volts.

Then from the above observations, we can define the ideal **Digital Logic Gate** as one that has a "LOW" level logic "0" of 0 volts (ground) and a "HIGH" level logic "1" of +5 volts and this can be demonstrated as:

Ideal Digital Logic Voltage Levels

Where the opening or closing of the switch produces either a logic level "1" or a logic level "0" with the resistor R being known as a "pull-up" resistor.

# 17. With circuit schematic and explain the operation and characteristics of a ECL gate. [CO1-L1].

**Emitter Coupled Logic** or **ECL** is another type of digital logic gate that uses bipolar transistor logic where the transistors are not operated in the saturation region, as they are with the standard TTL digital logic gate. Instead the input and output circuits are push-pull connected transistors with the supply voltage negative with respect to ground. This has the effect of increasing the speed of operation of the ECL gates up to the Gigahertz range compared with the standard TTL types, but noise has a greater effect in ECL logic, because the unsaturated transistors operate within their active region and amplify as well as switch signals.

# 18.Draw the CMOS logic circuit for NOR gate and explain its operation. [CO1-L1-Nov 2015]

One of the main disadvantages of the TTL logic series is that the gates are based on bipolar transistor logic technology and as transistors are current operated devices, they consume large amounts of power from a fixed +5 volt power supply. Also, TTL bipolar transistor gates have a limited operating speed when switching from an "OFF" state to an "ON" state and vice-versa called the "gate" or "propagation delay". To overcome these limitations

*Electronics and Communication Engineering Department* 32 *Digital Electronics*

complementary MOS called "CMOS" logic gates using "Field Effect Transistors" or FET's were developed.

As these gates use both P-channel and N-channel MOSFET's as their input device, at quiescent conditions with no switching, the power consumption of CMOS gates is almost zero, (1 to 2uA) making them ideal for use in low-power battery circuits and with switching speeds upwards of 100MHz for use in high frequency timing and computer circuits.

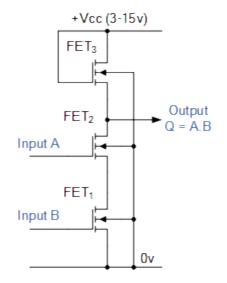

## 2-input NAND gate

This CMOS gate example contains 3 N-channel MOSFET's, one for each input  $FET_1$  and  $FET_2$  and one for the output  $FET_3$ . When both the inputs A and B are at logic level "0",  $FET_1$  and  $FET_2$  are both switched "OFF" giving an output logic "1" from the source of  $FET_3$ .

When one or both of the inputs are at logic level "1" current flows through the corresponding FET giving an output state at Q equivalent to logic "0", thus producing a NAND gate function.

Improvements in the circuit design with regards to switching speed, low power consumption and improved propagation delays has resulted in the standard CMOS 4000 "CD" family of logic IC's being developed that complement the TTL range.

As with the standard TTL digital logic gates, all the major digital logic gates and devices are available in the CMOS package such as the CD4011, a Quad 2-input NAND gate, or the CD4001, a Quad 2-input NOR gate along with all their sub-families. *Electronics and Communication Engineering Department* 33 *Digital Electronics*

Like TTL logic, complementary MOS (CMOS) circuits take advantage of the fact that both Nchannel and P-channel devices can be fabricated together on the same substrate material to form various logic functions. One of the main disadvantage with the CMOS range of IC's compared to their equivalent TTL types is that they are easily damaged by static electricity so extra care must be taken when handling these devices. Also unlike TTL logic gates that operate on single +5V voltages for both their input and output levels, CMOS digital logic gates operate on a single supply voltage of between +3 and +18 volts.

In the next tutorial about **Digital Logic Gates**, we will look at the digital Logic <u>AND Gate</u> function as used in both TTL and CMOS logic circuits as well as its Boolean Algebra definition and truth tables.

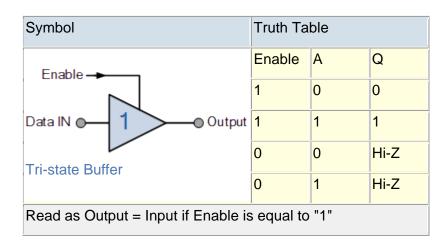

# 19. Explain "Tri-state Buffer" logic[CO1-L2].

A Tri-state Buffer can be thought of as an input controlled switch which has an output that can be electronically turned "ON" or "OFF" by means of an external "Control" or "Enable" signal input. This control signal can be either a logic "0" or a logic "1" type signal resulting in the Tri-state Buffer being in one state allowing its output to operate normally giving either a logic "0" or logic "1" output.

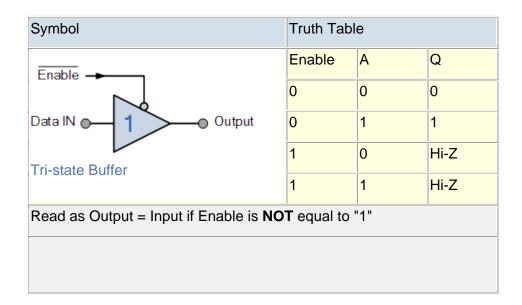

But when activated in the other state it disables or turns "OFF" its output producing an open circuit condition that is neither "High" or "low", but instead gives an output state of very high impedance, **high-Z**, or more commonly Hi-Z. Then this type of device has two logic state inputs, "0" or a "1" but can produce three different output states, "0", "1" or "Hi-Z" which is why it is called a "3-state" device. There are two different types of Tri-state Buffer, one whose output is controlled by an "**Active-HIGH**" control signal and the other which is controlled by an "**Active-LOW**" control signal, as shown below.

Active "HIGH" Tri-state Buffer

An **Active-high** Tri-state Buffer is activated when a logic level "1" is applied to its "**enable**" control line and the data passes through from its input to its output. When the enable control line is at logic level "0", the buffer output is disabled and a high impedance condition, Hi-Z is present on the output.Active "LOW" Tri-state Buffer is shown below.

An **Active-low** Tri-state Buffer is the opposite to the above, and is activated when a logic level "0" is applied to its "**enable**" control line. The data passes through from its input to its output. When the enable control line is at logic level "1", the buffer output is disabled and a high impedance condition, Hi-Z is present on the output.

#### Unit- II

# **Combinational Circuits**

# Part-A

# 1. How logic circuits of a digital system are classified? [CO2-L1].

Logic circuits of a digital system are classified into two types as combinational and sequential.

# 2. Define combinational logic[CO2-H3].

When logic gates are connected together to produce a specified output for certain specified combinations of input variables, with no storage involved, the resulting circuit is called combinational logic.

# 3. Write down the design procedure for combinational circuits[CO2-L1].

- The problem definition

- Determine the number of available input variables & required O/P variables.

- Assigning letter symbols to I/O variables

- Obtain simplified Boolean expression for each O/P.

- Obtain the logic diagram.

# 4. Define Half adder and full adder[CO2-L1].

The logic circuit that performs the addition of two bits is a half adder. The circuit that performs the addition of three bits is a full adder.

# 5. Define Decoder? [CO2-L1].

A decoder is a multiple - input multiple output logic circuit that converts coded inputs into coded outputs where the input and output codes are different.

# 6. What is binary decoder? [CO2-L1].

A decoder is a combinational circuit that converts binary information from n input lines to a maximum of 2n out puts lines.

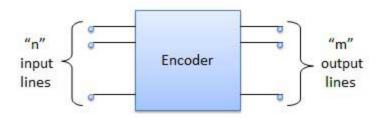

#### 7. Define Encoder? [CO2-L1].

An encoder has 2n input lines and n output lines. In encoder the output lines generate the binary code corresponding to the input value.

#### 8. What is priority Encoder? [CO2-L1].

A priority encoder is an encoder circuit that includes the priority function. In priority encoder, if 2 or more inputs are equal to 1 at the same time, the input having the highest priority will take precedence.

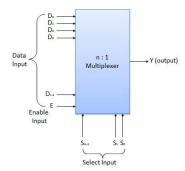

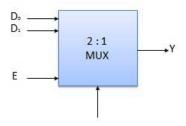

#### 9. Define multiplexer and draw the block diagram. [CO2-L1].

Multiplexer is a digital switch. If allows digital information from several sources to be routed onto a single output line.

#### 10. What do you mean by comparator? [CO2-L1].

A comparator is a special combinational circuit designed primarily to compare the relative magnitude of two binary numbers.

#### 11. What is a demux? [CO2-L1].

A decoder with an enable input is referred to as a demultiplexer.

#### 12. What is priority encoder? [CO2-L1].

A priority encoder is an encoder circuit that includes the priority function. The operation of the priority encoder is such that if two or more inputs are equal to 1 at the same time, the input having the highest priority will take precedence.

#### 13. How can a decoder be converted into a demultiplexer? [CO2-L1].

A decoder can be converted into a demultiplexer by including enable input.

Electronics and Communication Engineering Department 37 Digital Electronics

#### 14. What are tri-state gates? [CO2-L1].

A three-state gate is a digital circuit that exhibits three states. Two of the states are signals equivalent to logic 1 and logic 0 and the third state is a high impedance state.

#### 15. Distinguish between decoder and demultiplexer. [CO2-L1].

| Decoder                                           | Demultiplexer                                    |

|---------------------------------------------------|--------------------------------------------------|

| A decoder is a combinational circuit              | A demultiplexer is a circuit that                |

| that converts binary information from n           | receives information from a single line and      |

| input lines to a maximum of 2 <sup>n</sup> unique | transmits this information on one 2 <sup>n</sup> |

| output lines. It is sometimes called as n-to-     | possible output lines.                           |

| m-line decoder, where $m \le 2^n$ .               |                                                  |

|                                                   |                                                  |

## 16.How can a multiplexer be used to convert 8-bit parallel data into serial form? [CO2-L1].

- > A 8-to-1-line multiplexer is used to convert 8-bit parallel data into serial form.

- > Each of the eight inputs,  $I_0$  through  $I_7$ , is applied to one input of an AND gate.

- > Selection lines  $S_0$ ,  $S_1$ ,  $S_2$ , and  $S_3$  are decoded to select a particular AND gate.

- The outputs of the AND gates are applied to a single OR gate that provides the 1-line (serial form) output.

- > Consider the case when the selection lines  $S_2S_1S_0 = 011$ .

- The AND gate associated with input I<sub>3</sub> has three of its inputs equal to 1 and the third input connected to I<sub>3</sub>.

- The other seven AND gates have at least one input equal to 0, which makes their outputs equal to 0.

- The OR output is now equal to the value of I<sub>2</sub>, providing a path from the selected input to the output. Thus it converts 8-bit parallel data into a serial form.

*Electronics and Communication Engineering Department* 38 *Digital Electronics*

| $S_2$ | $\mathbf{S}_1$ | $\mathbf{S}_0$ | Y     |

|-------|----------------|----------------|-------|

| 0     | 0              | 0              | $I_0$ |

| 0     | 0              | 1              | $I_1$ |

| 0     | 1              | 0              | $I_2$ |

| 0     | 1              | 1              | $I_3$ |

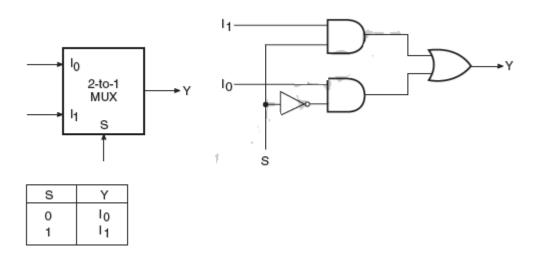

# 17. Draw a 2 to 1 multiplexer circuit. [CO2-L1].2 to 1 line Multiplexer

#### 18. What is a combinational circuit? Give an example[CO2-L1].

Combinational logic circuits are circuits in which the output at any time depends upon the combination of the input signals present at that instant only and does not depend upon the past conditions

Example:

- Decoder

- Multiplexer

*Electronics and Communication Engineering Department* 39 *Digital Electronics*

- Adder

- Subtractor

#### 19. What is meant by multilevel gate network? [CO2-L1].

The multilevel gate networks are 2 level, 3level, 4level gate network, etc. The maximum number of gates cascaded in series between a network input and the output is referred to as the number of levels of gates

## 20. What is look-ahead carry addition?(or) Suggest a solution to overcome the limitation on speed of an adder[CO2-L1].

The speed with which an addition is performed is limited by the time required for the carries to propagate or ripple through all of the adder. One method of speeding up the process is by eliminating the ripple carry delay and this is called look-ahead carry addition. This method is based on two functions of the full adder, called the carry generate and carry propagate function.

# 21. Draw the logic symbol and construct the truth table for two input EXOR gate[CO2-L1]..

Exclusive-OR gate

| Α | в | Output |

|---|---|--------|

| 0 | 0 | 0      |

| 0 | 1 | 1      |

| 1 | 0 | 1      |

| 1 | 1 | 0      |

|   |   |        |

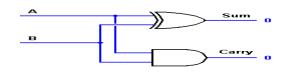

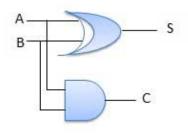

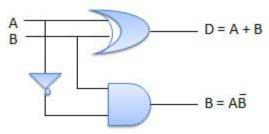

22. Draw the circuit of half adder and half subtractor[CO2-L1].

Half Adder:

#### Full adder:

23. Design an EXOR gates only using Nand gates[CO2-L1].

#### 1. Explain with a neat sketch Half Adder[CO2-L1].

Half adder is a combinational logic circuit with two inputs and two outputs. The half adder circuit is designed to add two single bit binary number A and B. It is the basic building block for addition of two single bit numbers. This circuit has two outputs carry and sum.

| Inpu | ts | Output |

|------|----|--------|

| А    | В  | S C    |

| 0    | 0  | 0 0    |

| 0    | 1  | 1 0    |

| 1    | 0  | 1 0    |

| 1    | 1  | 0 1    |

Circuit Diagram

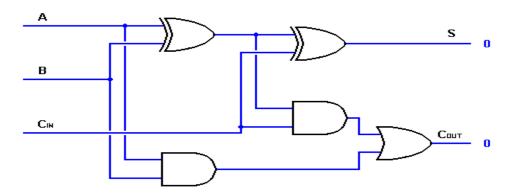

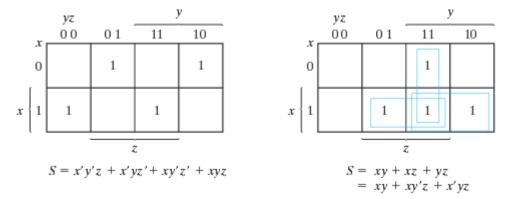

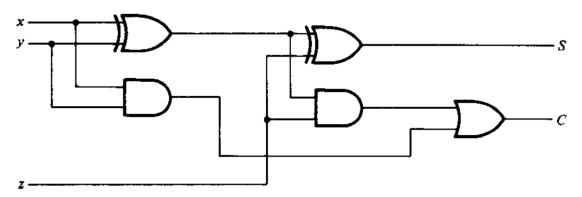

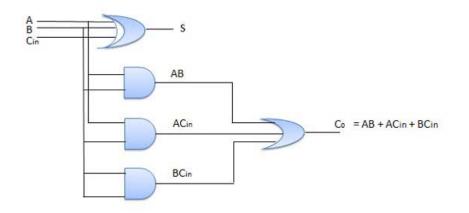

#### 2. Design a full adder using two half adders and an OR gate[CO2-L1].

A full adder is a combinational circuit that forms the arithmetic sum of three input bits. It consists of three inputs and two outputs. Two of the input variables, denoted by x and y, represent the two significant bits to be added. The third input z, represents the carry from the previous lower significant position.

**Step 1**: Determine the number of inputs and outputs.

**Step 2** :Draw the truth table for a full adder with three inputs x,y and zand two outputs S and  $C_{out.}$

Electronics and Communication Engineering Department 42 Digital Electronics

| Inputs |   | Outputs |     |                  |

|--------|---|---------|-----|------------------|

| х      | У | z       | Sum | C <sub>out</sub> |

| 0      | 0 | 0       | 0   | 0                |

| 0      | 0 | 1       | 1   | 0                |

| 0      | 1 | 0       | 1   | 0                |

| 0      | 1 | 1       | 0   | 1                |

| 1      | 0 | 0       | 1   | 0                |

| 1      | 0 | 1       | 0   | 1                |

| 1      | 1 | 0       | 0   | 1                |

| 1      | 1 | 1       | 1   | 1                |

Step 3 : Obtain the K map Simplification for Sum and Carry Out

#### Step 4 : Implementation

A full adder can be implemented with two half adders and one OR gate as shown in the Fig. The S output from the second half-adder is the exclusive-OR of Z and the output of the first half adder, giving

$$S = z \oplus (x \oplus y)$$

=  $z'(xy' + x'y) + z(xy' + x'y)'$

=  $z'(xy' + x'y) + z(xy + x'y')$

=  $xy'z' + x'yz' + xyz + x'y'z$

*Electronics and Communication Engineering Department* 43 *Digital Electronics*

and the carry output is

$$C = z(xy' + x'y) + xy = xy'z + x'yz + xy$$

Fig. Implementation of a full adder with two Half adders and an OR gate

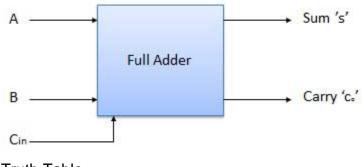

#### 3. Explain Full Adder with neat sketch[CO2-L2].

Full adder is developed to overcome the drawback of Half Adder circuit. It can add two one-bit numbers A and B, and carry c. The full adder is a three input and two output combinational circuit.

Block diagram

Truth Table

| 1 | Inputs | Output |      |

|---|--------|--------|------|

| А | В      | Cin    | S Co |

| 0 | 0      | 0      | 0 0  |

| 0 | 0      | 1      | 1 0  |

| 0 | 1      | 0      | 1 0  |

| 0 | 1      | 1      | 0 1  |

| 1 | 0      | 0      | 1 0  |

| 1 | 0      | 1      | 0 1  |

| 1 | 1      | 0      | 0 1  |

| 1 | 1      | 1      | 1 1  |

#### Circuit Diagram

#### 4. Design a Half Subtractor and explain its operation [CO2-H3].

Half subtractor is a combination circuit with two inputs and two outputs (difference and borrow). It produces the difference between the two binary bits at the input and also produces an output (Borrow) to indicate if a 1 has been borrowed. In the subtraction (A-B), A is called as Minuend bit and B is called as Subtrahend bit.

Truth Table

| Inpu | ts | Output  |        |

|------|----|---------|--------|

| А    | В  | (A – B) | Borrow |

| 0    | 0  | 0       | 0      |

| 0    | 1  | 1       | 1      |

| 1    | 0  | 1       | 0      |

| 1    | 1  | 0       | 0      |

Circuit Diagram

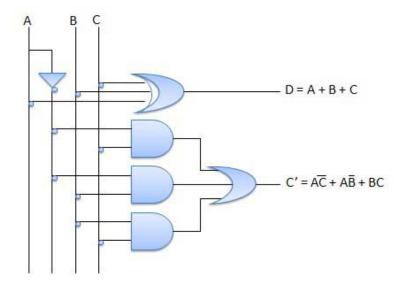

#### 5. Design a Full Subtractor circuit and explain its operation[CO2-H3].

The full subtractor is a combinational circuit with three inputs A,B,C and two output D and C'. A is the 'minuend', B is 'subtrahend', C is the 'borrow' produced by the previous stage, D is the difference output and C' is the borrow output.

Truth Table

|   | Inputs |   | Outp    | out |

|---|--------|---|---------|-----|

| А | в      | С | (A-B-C) | C'  |

| 0 | 0      | 0 | 0       | 0   |

| 0 | 0      | 1 | 1       | 1   |

| 0 | 1      | 0 | 1       | 1   |

| 0 | 1      | 1 | 0       | 1   |

| 1 | 0      | 0 | 1       | 0   |

| 1 | 0      | 1 | 0       | 0   |

| 1 | 1      | 0 | 0       | 0   |

| 1 | 1      | 1 | 1       | 1   |

Circuit Diagram

#### 6. Explain the operation of Multiplexer circuit[CO2-L2].

Multiplexer is a special type of combinational circuit. There are n-data inputs, one output and m select inputs with 2m = n. It is a digital circuit which selects one of the n data inputs and routes it to the output. The selection of one of the n inputs is done by the selected inputs. Depending on the digital code applied at the selected inputs, one out of n data sources is selected and transmitted to the single output Y. E is called the strobe or enable input which is useful for the cascading. It is generally an active low terminal that means it will perform the required operation when it is low.

Block diagram

Multiplexers come in multiple variations

• 2:1 multiplexer

*Electronics and Communication Engineering Department* 47

- 4:1 multiplexer

- 16 : 1 multiplexer

- 32 : 1 multiplexer

#### Block Diagram

#### Truth Table

| Enable | Select | Output |

|--------|--------|--------|

| E      | S      | Y      |

| 0      | x      | 0      |

| 1      | 0      | Do     |

| 1      | 1      | Dı     |

x = Don't care

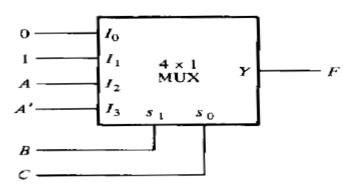

#### 7. Implement the given Boolean function using 8: 1 multiplexer[CO2-L1].

#### F (A, B, C) = ∑ (1, 3, 5, 6)

Step 1 : The given function can be implemented using a 4 x1 multiplexer

B and C inputs are connected to the Selection lines  $S_1$  and  $S_0$  respectively. Figures (a) shows the multiplexer implementation

Fig (a) Multiplexer implementation

*Electronics and Communication Engineering Department* 48 *Digital Electronics*

| Minterm | A   | B | С | F |

|---------|-----|---|---|---|

| 0       | 0   | 0 | 0 | 0 |

| 1       | 0   | 0 | 1 | 1 |

| 2       | 0   | 1 | 0 | 0 |

| 3       | 0   | 1 | 1 | 1 |

| 4       | 1   | 0 | 0 | 0 |

| 5       | I I | 0 | l | 1 |

| 6       | 1   | 1 | 0 | 1 |

| 7       | 1   | 1 | 1 | 0 |

Fig (b) Truth table

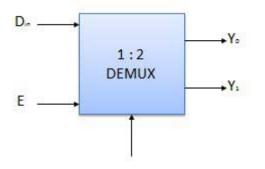

#### 8. Explain Demultiplexer[CO2-L2].

A demultiplexer performs the reverse operation of a multiplexer i.e. it receives one input and distributes it over several outputs. It has only one input, n outputs, m select input. At a time only one output line is selected by the select lines and the input is transmitted to the selected output line. A de-multiplexer is equivalent to a single pole multiple way switch as shown in fig.

Demultiplexers comes in multiple variations.

- 1:2 demultiplexer

- 1:4 demultiplexer

- 1:16 demultiplexer

Electronics and Communication Engineering Department

|    | $I_0$ | $I_1$        | $I_2$ | 13 |

|----|-------|--------------|-------|----|

| A' | 0     | $\mathbf{O}$ | 2     | 3  |

| A  | 4     | 3            | 6     | 7  |

|    | 0     | 1            | A     | A' |

#### (c) Implementation table

49 Digital Electronics

• 1:32 demultiplexer

#### Block diagram

#### Truth Table

| Enable | Select | Output |     |

|--------|--------|--------|-----|

| E      | S      | YO     | Y1  |

| 0      | x      | 0      | 0   |

| 1      | 0      | 0      | Dir |

| 1      | 1      | Din    | 0   |

x = Don't care

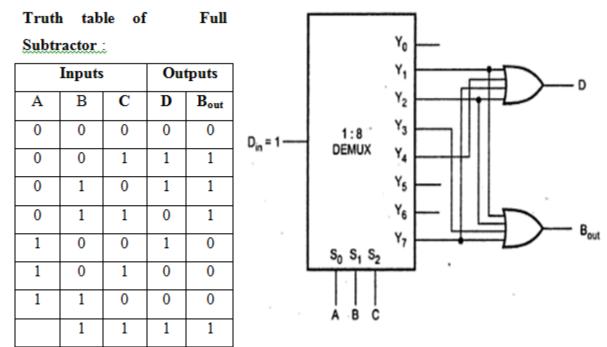

#### 9. Implement the full subtractor using demultiplexer[CO2-H1].

Step 1 : Write the truth table of full subtractor.

Step 2 : Represent output of full subtractor in minterm form.

For full subtractor, difference D function can be written as D =  $f(A,B,C) = \sum_{m} = (1,2,4,7)$  and the Borrow out can be written as  $B_{out} = f(A,B,C) = \sum_{m} = (1,2,3,7)$

Step 3 : Logically OR the outputs corresponding to minterms.

With  $D_0$  input 1, demultiplexer gives minterms at the output so by logically ORing the required minterms we can implement Boolean functions for full subtractor.

Fig. Full subtractor using 1: 8 Demux

#### 10. Explain Decoders and its types. [CO2-L2].

A decoder is a combinational circuit. It has n input and to a maximum m = 2n outputs. Decoder is identical to a demultiplexer without any data input. It performs operations which are exactly opposite to those of an encoder.

Block diagram

Examples of Decoders are following.

- Code converters

- BCD to seven segment decoders

- Nixie tube decoders

- Relay actuator

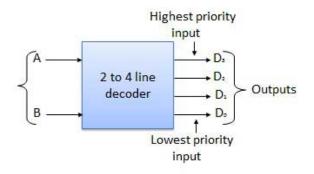

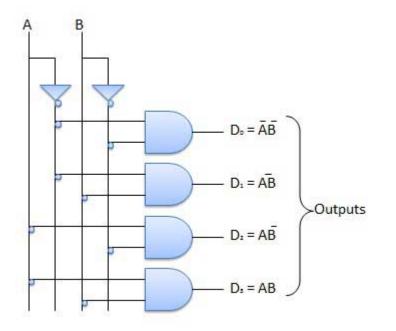

#### 2 to 4 Line Decoder

The block diagram of 2 to 4 line decoder is shown in the fig. A and B are the two inputs where D through D are the four outputs. Truth table explains the operations of a decoder. It shows that each output is 1 for only a specific combination of inputs.

#### Block diagram

#### Truth Table

| Inpu | its |    | Output |    |    |  |  |  |

|------|-----|----|--------|----|----|--|--|--|

| A    | В   | Do | D:     | D: | D, |  |  |  |

| 0    | 0   | 1  | 0      | 0  | 0  |  |  |  |

| 0    | 1   | 0  | 1      | 0  | 0  |  |  |  |

| 0    | 1   | 0  | 0      | 1  | 0  |  |  |  |

| 1    | 1   | 0  | 0      | 0  | 1  |  |  |  |

#### Logic Circuit

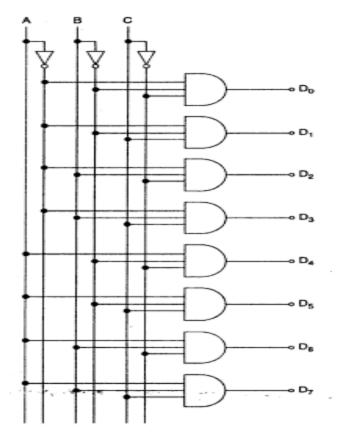

#### 11. Design a 3:8 decoder using basic gates. [CO2-H3].

A 3 to 8 decoder has three inputs(A,B,C) and eight outputs ( $D_0$  to  $D_7$ ). Based on the three inputs one of the eight outputs is selected. The Truth table for 3 to 8 Decoder is given below :

| Inputs |   |    | Outputs        |       |       |       |       |       |                |    |

|--------|---|----|----------------|-------|-------|-------|-------|-------|----------------|----|

| A,     | B | С  | D <sub>0</sub> | $D_I$ | $D_2$ | $D_3$ | $D_4$ | $D_5$ | D <sub>6</sub> | D7 |

| 0      | 0 | 0  | 1              | 0     | 0     | 0     | 0     | 0     | 0              | 0  |

| 0      | 0 | 1. | 0              | 1     | 0     | 0     | 0     | 0     | 0              | 0  |

| 0      | 1 | 0  | 0              | 0     | 1     | 0     | 0     | 0     | 0              | 0  |

| 0      | 1 | 1  | 0              | 0     | 0     | 1     | 0     | 0     | 0              | 0  |

| 1      | 0 | 0  | 0              | 0     | 0     | 0     | 1     | 0     | 0              | 0  |

| 1      | 0 | 1  | 0              | 0     | . 0   | 0     | 0     | 1     | 0              | 0  |

| 1      | 1 | 0  | 0              | 0     | 0.    | 0     | 0     | 0     | 1              | 0  |

| 1      | 1 | 1  | 0              | 0     | 0     | 0     | 0     | 0     | 0              | 1  |

#### Logic diagram of 3 to 8 Decoder:

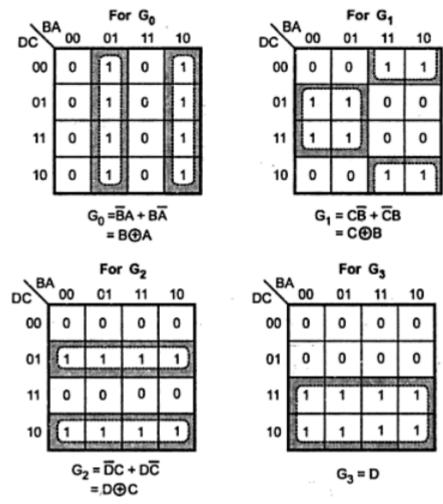

#### 12. Explain Encoders. [CO2-L2].

Encoder is a combinational circuit which is designed to perform the inverse operation of the decoder. An encoder has n number of input lines and m number of output lines. An encoder produces an m bit binary code corresponding to the digital input number. The encoder accepts an n input digital word and converts it into an m bit another digital word.

Block diagram

Examples of Encoders are following.

- Priority encoders

- Decimal to BCD encoder

- Octal to binary encoder

- Hexadecimal to binary encoder

#### 13. What is a code converter? State its types. [CO2-L1].

A code converter circuit will convert coded information in one form to a different coding form.

Types of code converters;

- (i) Binary to Gray code converter

- (ii) Gray to Binary code converter

- (iii) BCD to Excess 3 code converter

- (iv) Excess 3 to BCD converter

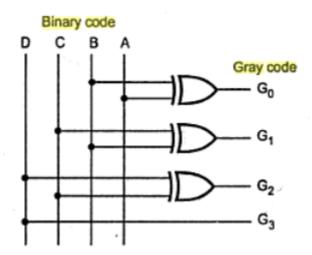

#### 14. Design a binary to gray code converter. [CO2-H3].

Step 1 : Form a truth table relating Binary code as input and Gray code as output.

| Decimal | Binary | y Code |   |   | Gray Code      |                |                       |                |

|---------|--------|--------|---|---|----------------|----------------|-----------------------|----------------|

|         | D      | С      | В | Α | G <sub>3</sub> | G <sub>2</sub> | <b>G</b> <sub>1</sub> | G <sub>0</sub> |

| 0       | 0      | 0      | 0 | 0 | 0              | 0              | 0                     | 0              |

| 1       | 0      | 0      | 0 | 1 | 0              | 0              | 0                     | 1              |

| 2       | 0      | 0      | 1 | 0 | 0              | 0              | 1                     | 1              |

| 3       | 0      | 0      | 1 | 1 | 0              | 0              | 1                     | 0              |

*Electronics and Communication Engineering Department* 55 *Digital Electronics*

| 4  | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |  |

|----|---|---|---|---|---|---|---|---|--|

| 5  | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 |  |

| 6  | 0 | 1 | 1 | 0 | 0 | 1 | 0 | 1 |  |

| 7  | 0 | 1 | 1 | 1 | 0 | 1 | 0 | 0 |  |

| 8  | 1 | 0 | 0 | 0 | 1 | 1 | 0 | 0 |  |

| 9  | 1 | 0 | 0 | 1 | 1 | 1 | 0 | 1 |  |

| 10 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 |  |

| 11 | 1 | 0 | 1 | 1 | 1 | 1 | 1 | 0 |  |

| 12 | 1 | 1 | 0 | 0 | 1 | 0 | 1 | 0 |  |

| 13 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 |  |

| 14 | 1 | 1 | 1 | 0 | 1 | 0 | 0 | 1 |  |

| 15 | 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 |  |

|    |   |   |   |   |   |   |   |   |  |

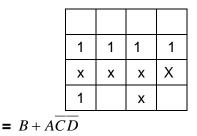

Step 2 : Perform K map simplification for each gray code output.

56

Step 3 : Realization of code converter using XOR gate.

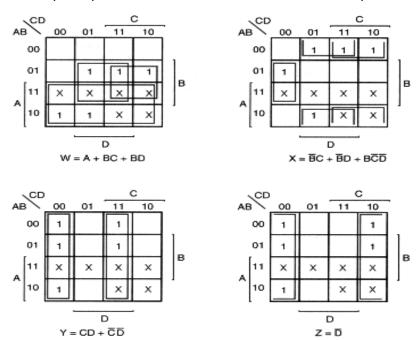

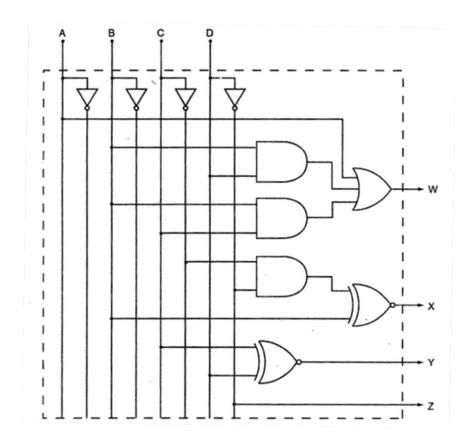

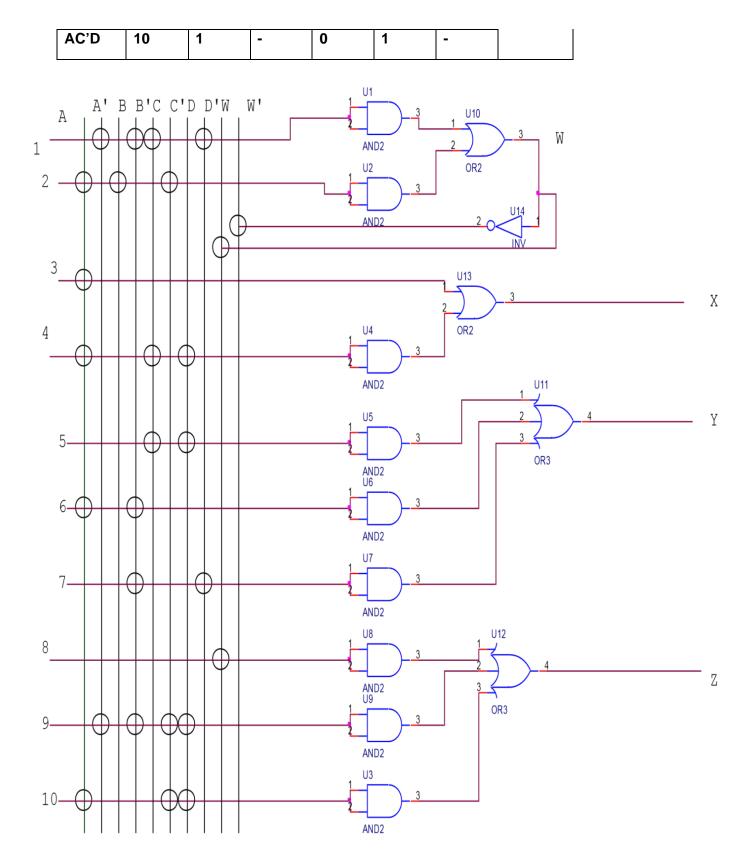

15. Design a four bit BCD to excess-3 code converter. Draw the logic diagram. [CO2-H3].

Step 1 : Form a truth table relating BCD code and Excess-3 code.

| Decimal |     | Inputs |   |   |   | Out | puts |   |

|---------|-----|--------|---|---|---|-----|------|---|

| number  | A   | B      | С | D | W | X   | Y    | 2 |

| 0       | 0   | 0      | 0 | 0 | 0 | 0   | 1    | 1 |

| 1       | 0   | 0      | 0 | 1 | 0 | 1   | 0    | 0 |

| 2       | 0   | 0      | 1 | 0 | 0 | 1   | 0    | 1 |

| 3       | 0   | 0      | 1 | 1 | 0 | 1   | 1    | 0 |

| 4       | 0   | 1      | 0 | 0 | 0 | 1   | 1    | 1 |

| 5       | 0   | 1      | 0 | 1 | 1 | 0   | 0    | 0 |

| 6       | 0   | 1      | 1 | 0 | 1 | 0   | 0    | 1 |

| 7       | 0   | 1      | 1 | 1 | 1 | 0   | 1    | 0 |

| 8       | 1   | 0      | 0 | 0 | 1 | 0   | 1    | 1 |

| 9       | 1   | 0      | 0 | 1 | 1 | 1   | 0    | 0 |

| 10      | 1   | 0      | 1 | 0 | d | d   | d    | d |

| 11      | 1   | 0      | 1 | 1 | d | d   | d    | d |

| 12      | 1   | 1      | 0 | 0 | d | d   | d    | d |

| 13      | 1   | 1      | 0 | 1 | d | d   | d    | d |

| 14      | 1 . | 1      | 1 | 0 | d | d   | d    | d |

| 15      | 1   | 1      | 1 | 1 | d | d   | d    | a |

*Electronics and Communication Engineering Department* 57

Digital Electronics

Step 2 : K map simplification for each Excess-3 code output

Step 3 : Realization of Code converter

#### Unit -III

#### Sequential Circuits

#### Part-A

#### 1. What is the classification of sequential circuits? [CO3-L1].

The sequential circuits are classified on the basis of timing of their signals into two types. They are,

- 1) Synchronous sequential circuit.

- 2) Asynchronous sequential circuit.

#### 2. Define Flip flop. ? [CO3-L1].

The basic unit for storage is flip flop. A flip-flop maintains its output state either at 1 or 0 until directed by an input signal to change its state.

#### 3. What are the different types of flip-flop? ? [CO3-L1].

There are various types of flip flops. Some of them are mentioned below they are,

- RS flip-flop

- SR flip-flop

- D flip-flop

- JK flip-flop

- T flip-flop

#### 4. Define race around condition. [CO3-L1].

In JK flip-flop output is fed back to the input. Therefore change in the output results change in the input. Due to this in the positive half of the clock pulse if both J and K are high then output toggles continuously. This condition is called 'race around condition'.

#### 5. What is edge-triggered flip-flop? [CO3-L1].

*Electronics and Communication Engineering Department* 60 *Digital Electronics*

The problem of race around condition can solved by edge triggering flip flop. The term edge triggering means that the flip-flop changes state either at the positive edge or negative edge of the clock pulse and it is sensitive to its inputs only at this transition of the clock.

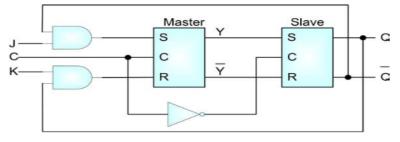

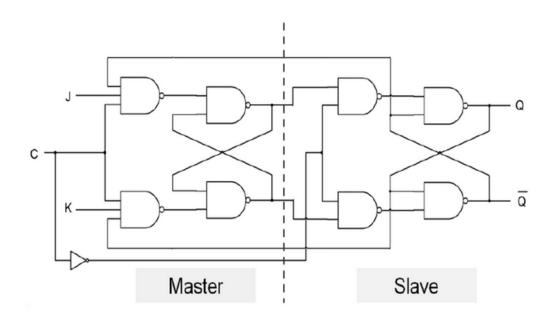

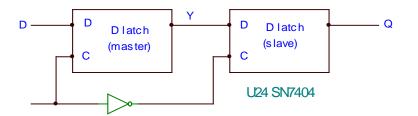

#### 6. What is a master-slave flip-flop? [CO3-L1]

A master-slave flip-flop consists of two flip-flops where one circuit serves as a master and the other as a slave.

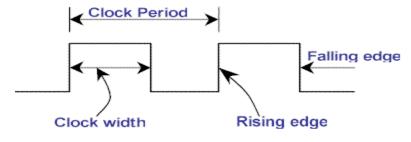

#### 7. Define rise time & fall time . [CO3-L1]

The time required to change the voltage level from 10% to 90% is known as rise time ( $t_r$ ). The time required to change the voltage level from 90% to 10% is known as fall time ( $t_f$ ).

#### 8. Define skew and clock skew. [CO3-L1]

The phase shift between the rectangular clock waveforms is referred to as skew and the time delay between the two clock pulses is called clock skew.

#### 9. Define setup time. [CO3-L1]

The setup time is the minimum time required to maintain a constant voltage levels at the excitation inputs of the flip-flop device prior to the triggering edge of the clock pulse in order for the levels to be reliably clocked into the flip flop. It is denoted as  $t_{setup}$ .

#### 10. Define hold time. [CO3-L1]

The hold time is the minimum time for which the voltage levels at the excitation inputs must remain constant after the triggering edge of the clock pulse in order for the levels to be reliably clocked into the flip flop. It is denoted as  $t_{hold}$ .

#### 11. Define propagation delay. [CO3-L1]

A propagation delay is the time required to change the output after the application of the input. It is denoted as  $t_{pd.}$

#### 12. Define registers. [CO3-L1]

*Electronics and Communication Engineering Department* 61 *Digital Electronics*

A register is a group of flip-flops flip-flop can store one bit information. So an n-bit register has a group of n flip-flops and is capable of storing any binary information/number containing n-bits.

#### 13. Define shift registers.

The binary information in a register can be moved from stage to stage within the register or into or out of the register upon application of clock pulses. This type of bit movement or shifting is essential for certain arithmetic and logic operations used in microprocessors. This gives rise to group of registers called shift registers.

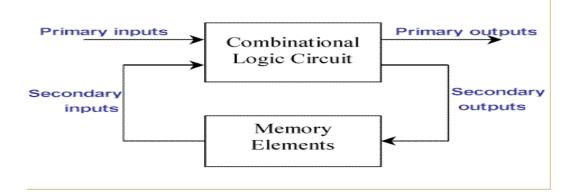

#### 14. Define sequential circuit?

In sequential circuits the output variables dependent not only on the present input variables but they also depend up on the past history of these input variables.

| Combinational circuits                    | Sequential circuits                  |

|-------------------------------------------|--------------------------------------|

| Memory unit is not required               | Memory unity is required             |

| Parallel adder is a combinational circuit | Serial adder is a sequential circuit |

#### 16. What do you mean by present state?

The information stored in the memory elements at any given time defines the present state of the sequential circuit.

#### 17. What do you mean by next state?

The present state and the external inputs determine the outputs and the next state of the sequential circuit.

#### 18. State the types of sequential circuits?

- 1. Synchronous sequential circuits

- 2. Asynchronous sequential circuits

#### 19. Define synchronous sequential circuit

Electronics and Communication Engineering Department 62 Digital Electronics

In synchronous sequential circuits, signals can affect the memory elements only at discrete instant of time.

#### 20. Define Asynchronous sequential circuit. [CO3-L1]

In asynchronous sequential circuits change in input signals can affect memory element at any instant of time.

#### 21. Draw the Block diagram of sequential circuit. [CO3-L1]

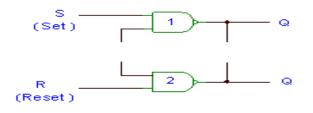

#### 22. Draw the logic diagram for SR latch using two NOR gates. [CO3-L1]

# 23. What are the types of shift register?(or) Classify the registers with respect to serial in parallel input output? [CO3-L1]

1. Serial in serial out shift registerElectronics and Communication Engineering Department63Digital Electronics

- 2. Serial in parallel out shift register

- 3. Parallel in serial out shift register

- 4. Parallel in parallel out shift register

- 5. Bidirectional shift register shift register

#### 24. State the types of counter? [CO3-L1]

- 1. Synchronous counter

- 2. Asynchronous Counter

25. The t pd for each flip-flop is 50 ns. Determine the maximum operating frequency for MOD -32 ripple counter [CO3-L1]

$f_{max (ripple)} = 5 \times 50 \text{ ns} = 4 \text{ MHZ}$

#### 26. What is the function of Universal shift Register? [CO3-L1]

The function of shift register is to shift the data in both directions and also to accept the data in parallel.

#### 27. How many Flip flops are required to design mod-10 counter? [CO3-L1]

The number of flip flops required to design mod 10 counter is 4.

(Since  $2^4 = 16$ )

#### 28. Give the exicitation for JK flipflop. [CO3-L1]

| Q   | $Q_{next}$ | J | K |

|-----|------------|---|---|

| 0   | 0          | 0 | X |

| 0   | 1          | 1 | X |

| 1   | 0          | X | 1 |

| _ 1 | 1          | X | 0 |

#### 29. What is Priority Encoder? [CO3-L1]

The priority encoder is an encoder that includes priority function. In the priority encoder if two or more inputs are equal to 1 at the same time, the inputs having the highest priority will take precedence.

*Electronics and Communication Engineering Department* 64 *Digital Electronics*

#### 30. Write down the characteristic equation of JK Flipflop. [CO3-L1]

The characteristic equation of JK Flipflop is

Q<sub>n+1</sub>=J+KQ

#### 31. What is meant by programmable counter? Mention its application. [CO3-L1]

A counter that divides the input frequency by a number which can be programmed, is called programmable counter.

#### **Applications:**

- 1. Frequency division.

- 2. Digital Clock.

- 3. Stop Watch.

- 4. Programmable Logic Counters.

#### 32. Write down the difference between Moore and Mealy model. [CO3-L1]

| S.No | Moore Model                                                                    | Mealy Model                                                           |

|------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 1    | Its output is a function of present state only.                                | Its output is a function of present state as well as present input.   |

| 2    | Input changes do not affect the output.                                        | Input changes may affect the output of the circuit.                   |

| 3    | Moore model requires more number of states for implementing the same function. | It requires less number of states for implementing the same function. |

#### Part-B

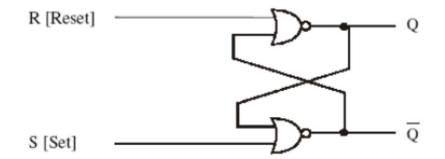

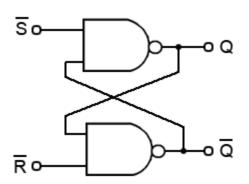

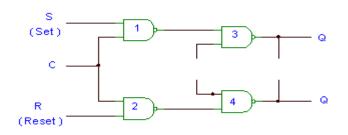

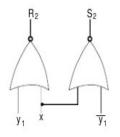

#### 1. Explain the circuit of a SR flip-flop and explain its operation. [CO3-L2]

The SR (Set-Reset) flip-flop is one of the simplest sequential circuits and consists of two gates connected as shown in Fig. 5.2.1. Notice that the output of each gate is connected to one of the inputs of the other gate, giving a form of positive feedback or 'cross-coupling'. The circuit has two active low inputs marked S and R, 'NOT' being indicated by the bar above the letter, as well as two outputs, Q and Q. Table shows what happens to the Q and Q outputs when a logic 0 is applied to either the S or R inputs.

|    | Table 5.2.1 |   |   |   |                                                                           |  |  |  |  |

|----|-------------|---|---|---|---------------------------------------------------------------------------|--|--|--|--|

|    | s           | R | đ | 9 | Comments                                                                  |  |  |  |  |

| 1. | 0           | 1 | 1 | 0 | Q is set to 1 by 0 on S                                                   |  |  |  |  |

| 2. | 1           | 1 | 1 | 0 | No change, (1 on Q is remembered)                                         |  |  |  |  |