## **SKP Engineering College**

Tiruvannamalai – 606611

A Course Material

on

**Electronic Circuits I**

By

**M.Jerin Jose**

**Assistant Professor**

**Electronics and Communication Engineering Department**

#### **Quality Certificate**

This is to Certify that the Electronic Study Material

Subject Code: EC6301

Subject Name: Electronic Circuits I

Year/Sem: II/ III

Being prepared by me and it meets the knowledge requirement of the University curriculum.

Signature of the Author Name: M.Jerin Jose

Designation: Assistant Professor

This is to certify that the course material being prepared by Mr. M.Jerin Jose is of the adequate quality. He has referred more than five books and one among them is from abroad author.

| Signature of HD         | Signature of the Principal     |

|-------------------------|--------------------------------|

| Name:Mr.R.Saravanakumar | Name: Dr.V.Subramania Bharathi |

| Seal:                   | Seal:                          |

#### EC6304 Electronic circuits I

#### Objective:

- To Learn about Biasing of BJTs and FETs.

- To Design and construct the Small Signal model of BJT Amplifiers.

- To Design and construct the Small Signal model of FET Amplifiers.

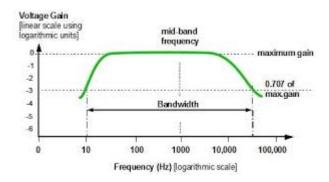

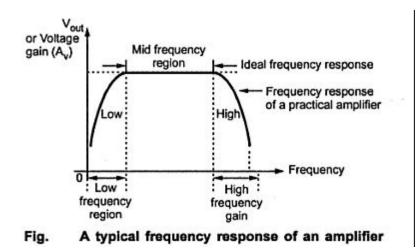

- To Study about the Frequency response of Amplifiers.

- To Design and Construct amplifiers with active loads

### UNIT I BIASING OF DISCRETE BJT AND MOSFET

Rectifiers with Filters -DC Load line, operating point, various biasing methods for BJT Design-Stability-Bias compensation, Thermal stability, Design of biasing for JFET, Design of biasing for MOSFET.

#### UNIT II BJT AMPLIFIERS

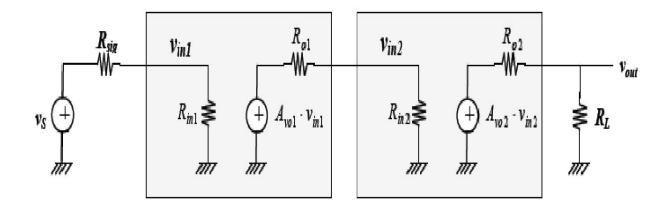

Small signal Analysis of Common Emitter-AC Load line, Voltage swing limitations, Common collector and common base amplifiers – Differential amplifiers- CMRR-Darlington Amplifier- Bootstrap technique - Cascaded stages - Cascode Amplifier.Large signal Amplifiers-Class A, Class B and Class C power Amplifiers.

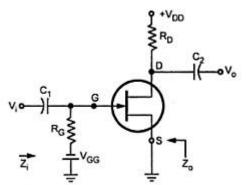

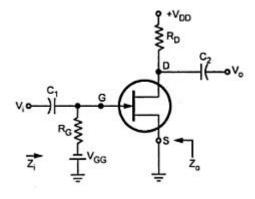

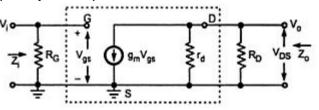

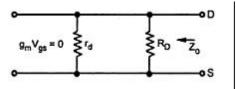

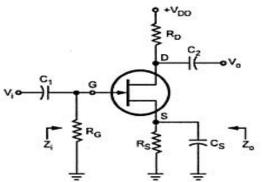

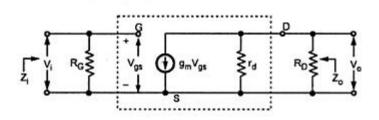

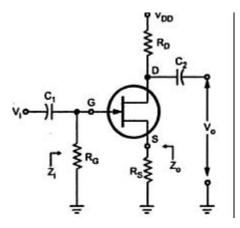

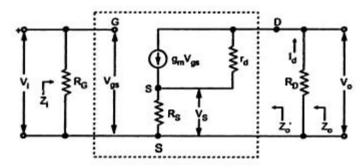

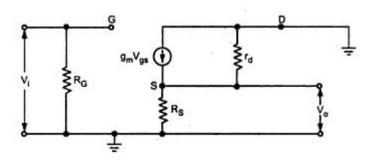

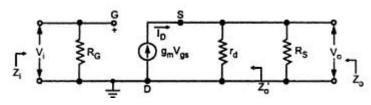

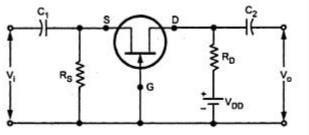

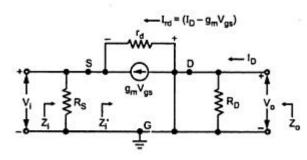

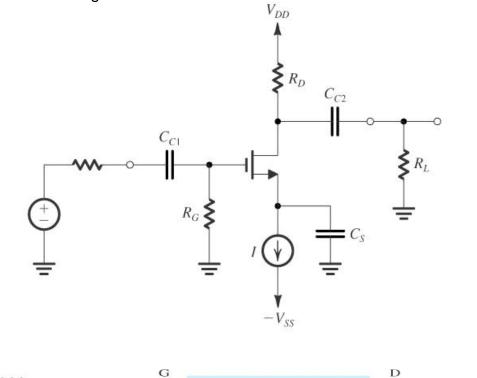

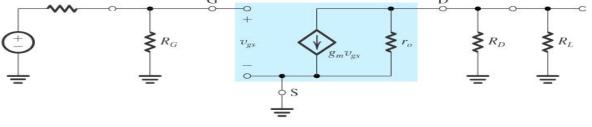

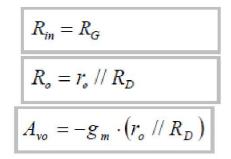

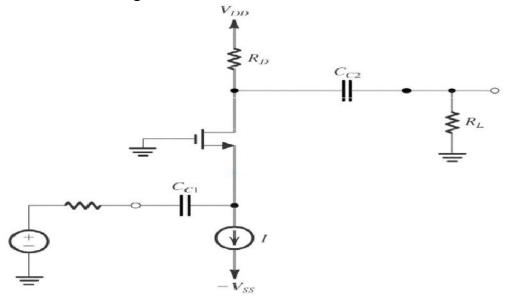

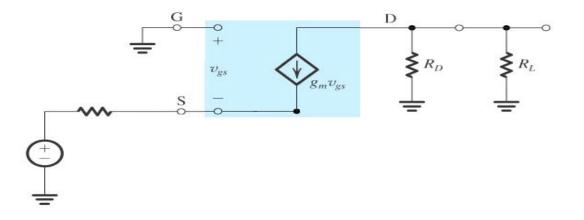

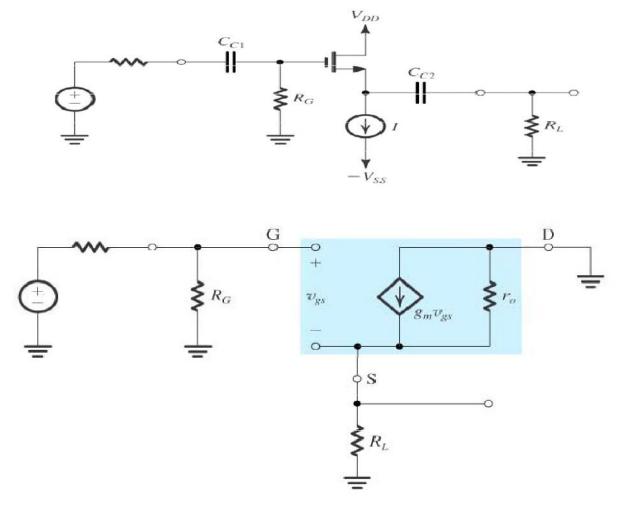

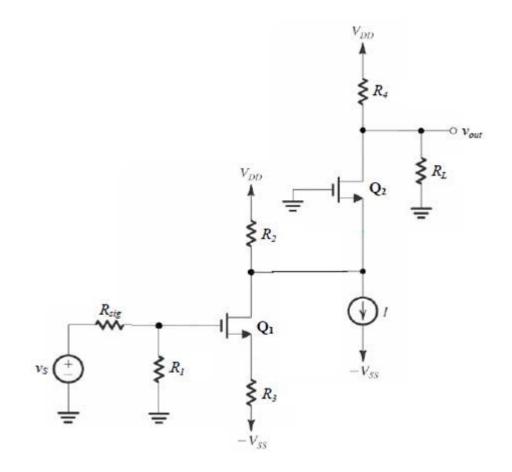

#### UNIT III JFET AND MOSFET AMPLIFIERS

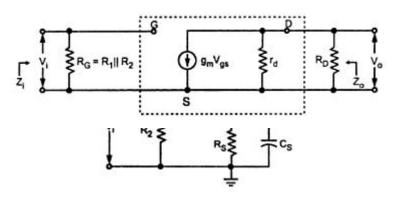

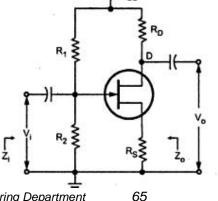

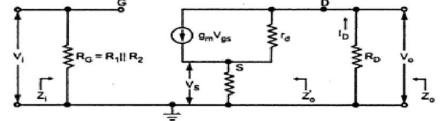

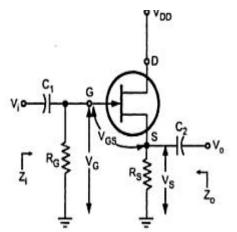

Small signal analysis of JFET amplifiers- Small signal Analysis of MOSFET and JFET, Common source amplifier, Voltage swing limitations, Small signal analysis of MOSFET and JFET Source follower and Common Gate amplifiers, - BiMOS Cascode amplifier.

#### UNIT IV FREQUENCY ANALYSIS OF BJT AND MOSFET AMPLIFIERS

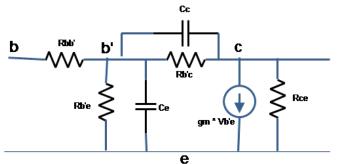

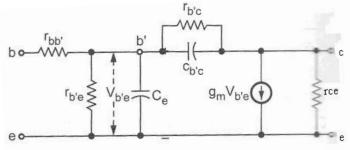

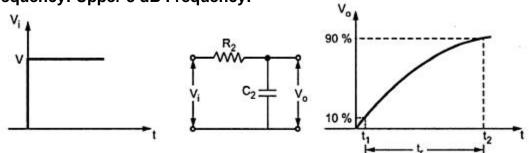

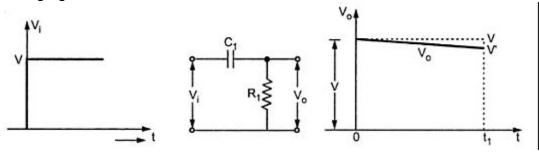

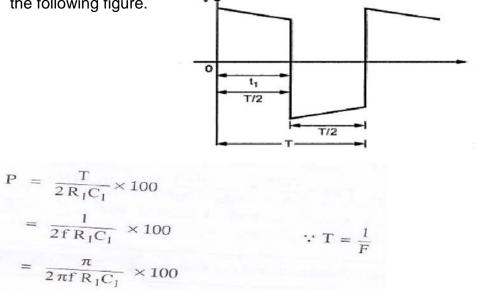

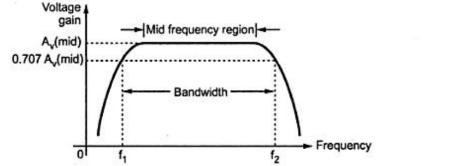

Low frequency and Miller effect, High frequency analysis of CE and MOSFET CS amplifier, Short circuit current gain, cut off frequency –  $f\alpha$  and  $f\beta$  unity gain and Determination of bandwidth of single stage and multistage amplifiers.

#### UNIT V IC MOSFET AMPLIFIERS

IC Amplifiers- IC biasing Current steering circuit using MOSFET- MOSFET current sources- PMOS and NMOS current sources. Amplifier with active loads - enhancement load, Depletion load and PMOS and NMOS current sources load- CMOS common source and source follower- CMOS differential amplifier-CMRR.

#### OUTCOMES:

### Upon Completion of the course, the students will be able to:

• design various biasing circuits for all the type of transistors to keep the operating point Stable.

3

- design and analyze the small signal equivalent circuits of BJT Amplifiers

- design and analyze the small signal equivalent circuits of FET Amplifiers

- design and analyze the Frequency Response of Amplifiers

#### Electronic Circuits I

LTPC3003

9

9

• design and analyze the different types of current mirror used for biasing.

#### **TEXT BOOK**

1. Donald .A. Neamen, Electronic Circuit Analysis and Design –2nd Edition, Tata Mc Graw Hill, 2009.

#### **REFERENCES**:

2.Adel .S. Sedra, Kenneth C. Smith, "Micro Electronic Circuits", 6th Edition, Oxford University Press, 2010.

3.David A., "Bell Electronic Devices and Circuits", Oxford Higher Education Press, 5th Editon, 2010

4.Behzad Razavi, "Design of Analog CMOS Integrated Circuits", Tata Mc Graw Hill, 2007.

5.Paul Gray, Hurst, Lewis, Meyer "Analysis and Design of Analog Integrated Circuits", 4thEdition ,John Willey & Sons 2005.

6.Millman.J. and Halkias C.C, "Integrated Electronics", Mc Graw Hill, 2001.

7.D.Schilling and C.Belove, "Electronic Circuits", 3rd Edition, Mc Graw Hill, 1989.

8.Robert L.Boylestad and Louis Nasheresky,"Electronic Devices and Circuit Theory", 10<sup>th</sup> Edition,peaeson Education/PHI,2008

4

9. http://nptel.ac.in

10. <u>http://freevideolectures.com/Course/2312/Basic-Electronics/15#</u>

#### CONTENTS

| S.No | Particulars | Page |

|------|-------------|------|

| 1    | Unit – I    | 6    |

| 2    | Unit – II   | 18   |

| 3    | Unit – III  | 59   |

| 4    | Unit – IV   | 80   |

| 5    | Unit – V    | 118  |

#### Unit- I

#### Biasing Of Discrete BJT and MOSFET

#### Part- A

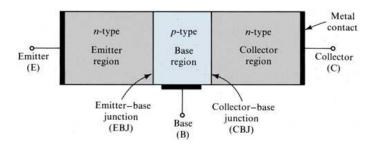

#### 1. Describe about BJT? [CO1-L1]

BJT consists of 2 PN junctions. It has three terminals: emitter, base and collector. Transistor can be operated in three regions, namely cut-off, active and saturation by applying proper biasing conditions.

### 2. List the operating regions of the transistor [CO1-L2]

Active:

- Most important mode, e.g. for amplifier operation and switching application

- The region where current curves are practically flat.

Saturation:

Barrier potential of the junctions cancels each other out causing a virtual short.

- Ideal transistor behaves like a closed switch.

Cutoff:

- Current reduced to zero

- Ideal transistor behaves like an open switch.

#### 3. What is need of biasing? [CO1-L1]

Bias establishes the DC operating point for proper linear operation of an amplifier. If an amplifier is not biased with correct DC voltages on the input and output, it can go into saturation or cutoff when an input signal is applied.

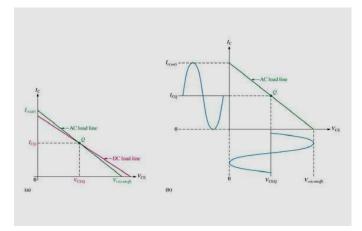

#### 4. Why do we choose Q point at the center of the load line? [CO1-L13

The output signal is sinusoidal waveform without any distortion. Thus point Q is the best operating point.

### 5. Name the two techniques used in the stability of the q point. [CO1-L2] Stabilization technique:

It refers to the use of resistive biasing circuits which allow  $I_B$  to vary so as to keep  $I_C$  relatively constant with variations in  $I_{CO}$ ,  $\beta$  and  $V_{BE}$ .

#### **Compensation technique:**

It refers to the use of temperature sensitive devices such as diodes, transistors, thermistors which provide compensating voltage and current to maintain Q point stable.

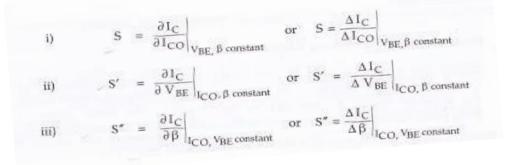

#### 6. Give the expression for stability factor? [CO1-L3]

It is defined as the degree of change in operating point due to variation in temperature. There are three variables which are temperature dependent. Three stability factors are defined as follows,

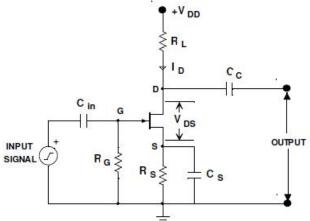

#### 7. What is meant by FET biasing? [CO1-L1]

- The Parameters of FET is temperature dependent .When temperature increases drain resistance also increases, thus reducing the drain current.

- Unlike BJTs, thermal runaway does not occur with FET

- $\bullet$  However, the wide differences in maximum and minimum transfer characteristics make  $I_D$  levels unpredictable with simple fixed-gate bias

#### 8. What are the different biasing circuits? [CO1-L1]

- Fixed bias circuits

- Self bias circuits

- Voltage bias circuits

#### 9. What are the requirements of a biasing circuit? [CO1-L2]

- a. Emitter base junction must be forward biased and collector base junction must be reverse biased. That means the transistor should be operated in the middle of the active region or Q point should be fixed at the centre of the active region.

- b. Circuit design should provide a degree of temperature stability.

- c. Q point should be made independent of the transistor parameters such as  $\beta$ .

#### 10. Merits of stability factor? [CO1-L2]

- It is simple to shift the operating point anywhere in the active region by merely changing the base resistor (R<sub>B</sub>).

- A very small number of components are required.

#### 11 Define operating point. (May, 15) [CO1-L1]

The zero signal values of Ic & Vce are known as operating point. It is also called so because the variations of Ic and Vce take place about this point, when the signal is applied.

#### Why the operating point is selected at the centre of the active

#### 12 region? [CO1-L1]

The operating point of a transistor is kept fixed usually at the center of the active region

in order that the input signal is well amplified. If the point is fixed in the saturation region or

the cut off region the positive and negative half cycle gets clipped off respectively.

#### 13 What is DC load line? [CO1-L1]

It is the line on the output characteristics of a transistor circuit which gives the values of Ic & Vce corresponding to zero signal (or) DC Conditions.

#### 14 What is the need for biasing in transistor amplifier? [CO1-L1]

The proper flow of zero signal collector current and the maintenance of proper collector emitter voltage during the passage of signal is known as transistor biasing.

S.K.P. Engineering College, Tiruvannamalai

When a transistor is biased properly, it works efficiently and produces no distortion in the output signal and thus operating point can be maintained stable.

### 15. What are the factors to be considered to design a biasing circuit? (May,15) [CO1-L1]

It should ensure proper zero signal collector current.

The emitter base junction must be forward biased and collector base junction must be reversing biased.

The transistor should be operated in the middle of the active region or operation point should be fixed at the centre of the active region.

The operating point should be made independent of the transistor parameters (such as  $\beta$ ). It should ensure that *VCE* does not fall below 0.5 V for *Ge* transistors and 1 V for

silicon transistors at any instant.

#### 16. List out different type of biasing. [CO1-L1]

- i. Voltage divider bias

- ii. Fixed bias

- iii. Emitter feedback bias

- iv. Collector feedback bias

#### 17. Define stability factor of an amplifier. What is ideal value? [CO1-L2]

The rate of change of collector current IC w.r.t. the collector leakage current \*ICO at constant  $\beta$  and IB is called **stability factor** i.e.

Stability factor,  $S = dI_C / Ico dI at constant I_B and \beta$

### 18. What is thermal run away in a transistor? (Nov/Dec 2006) (Nov/Dec 2008) [CO1-L1]

The collector current, being equal increases with increase in temperature .This leads to increased power dissipation with further increase in temperature. .Being accumulative process it can lead to thermal runaway resulting in burn out of transistor. Self destruction of an un-stabilized transistor is called thermal runaway.

#### 19. Why thermal runaway is not there in FETs? [CO1-L2]

The FET has a positive temperature coefficient of resistivity. In FET, as temperature increases its drain resistance also increases, reducing the drain current. Thus, unlike BJT, thermal runaway does not occur with FET.

# 20. What are the advantages and disadvantages of fixed bias circuits? [CO1-L1]

Merits:

• It is simple to shift the operating point anywhere in the active region by merely changing the base resistor (R<sub>B</sub>).

• A very small number of components are required.

#### **Demerits:**

• The collector current does not remain constant with variation in temperature or power supply voltage. Therefore the operating point is unstable.

- Changes in  $V_{be}$  will change  $I_B$  and thus cause  $R_E$  to change. This in turn will alter the gain of the stage.

• When the transistor is replaced with another one, considerable change in the value of  $\beta$  can be expected. Due to this change the operating point will shift.

• For small-signal transistors (e.g., not power transistors) with relatively high values of  $\beta$  (i.e., between 100 and 200), this configuration will be prone to thermal runaway. In particular, the stability factor, which is a measure of the change in collector current with changes in reverse saturation current, is approximately  $\beta$ +1. To ensure absolute stability of the amplifier, a stability factor of less than 25 is preferred, and so small-signal transistors have large stability factors.

#### 21. How self-bias circuit is used as constant current source? [CO1-L1]

In the self bias circuit if Ic tends to increase because of ICO has increasing as a result of temperature, the current in RE increases. As consequences of the increase in voltage drop across RE that provides negative feedback, the base current is decreased. Hence constant IC value is maintained in the self bias circuit.

#### 22. How FET is known as Voltage variable resistor? [CO1-L2]

In the region before pinch off, where VDS is small, the drain to source resistance rd can be controlled by the bias voltage VGS. Therefore FET is useful as voltage variable resistor (VVR) or Voltage dependent Resistor (VDR)

#### PART-B

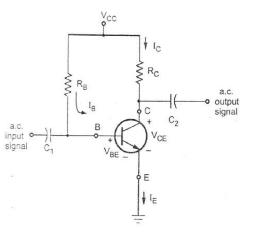

1. Explain the fixed bias method & derive an expression for stability factors. [CO1-H1]

The Figure shows the fixed bias circuit. It is the simplest d.c. bias configuration. For the d.c. analysis we can replace capacitor with an open circuit because the reactance of a capacitor for dc. is

$$X_{\rm C} = 1 / 2\pi \, {\rm fC} = 1 / 2\pi (0) \, {\rm C} = \infty.$$

In the base circuit, Apply KVL, we get

Therefore,

$I_{\rm B} = (V_{\rm CC} - V_{\rm BE})/R_{\rm B}$

For a given transistor,  $V_{BE}$  does not vary significantly during use. As  $V_{CC}$  is of fixed value, on selection of  $R_B$ , the base current  $I_B$  is fixed. Therefore this type is called *fixed bias* type of circuit.

#### In the Collector circuit

Apply KVL, we get

$$V_{CC} = I_C R_C + V_{CE}$$

Therefore,

The common-emitter current gain of a transistor is an important parameter in circuit design, and is specified on the data sheet for a particular transistor. It is denoted as  $\beta$ .

$$I_C = \beta I_B$$

$$I_{C} = \frac{V_{CC} - V_{CE}}{R_{C}}$$

$$V_{CE} = V_{C} - V_{E}$$

$$V_{BE} = V_{B} - V_{E}$$

In this circuit  $V_E = 0$

$$V_{BE} = V_B$$

$$V_{CE} = V_C$$

Stability factor S for Fixed bias circuit

**Stability Factor S**

$$I_{B} \cong \frac{V_{CC}}{R_{B}}$$

When  $I_B$  changes by  $\partial I_B$ ,  $V_{CC}$  and  $V_{BE}$  are unaffected.

$\therefore \frac{\partial I_B}{\partial I_C} = 0 \quad \because I_C \text{ is not present in the equation.}$

Substituting this value in equation , we get,

$$S = \frac{1+\beta}{1-\beta(\partial I_B / \partial I_C)} = \frac{1+\beta}{1-0}$$

$$S = 1+\beta$$

#### **Merits:**

- It is simple to shift the operating point anywhere in the active region by merely changing the base resistor (R<sub>B</sub>).

- A very small number of components are required.

#### **Demerits:**

- The collector current does not remain constant with variation in temperature or power supply voltage. Therefore the operating point is unstable.

- Changes in  $V_{be}$  will change  $I_B$  and thus cause  $R_E$  to change. This in turn will alter the gain of the stage.

- When the transistor is replaced with another one, considerable change in the value of  $\beta$  can be expected. Due to this change the operating point will shift.

- For small-signal transistors (e.g., not power transistors) with relatively high values of  $\beta$  (i.e., between 100 and 200),

This configuration will be prone to thermal runaway. In particular, the stability factor,

#### S.K.P. Engineering College, Tiruvannamalai

which is a measure of the change in collector current with changes in reverse saturation current, is approximately  $\beta$ +1. To ensure absolute stability of the amplifier, a stability factor of less than 25 is preferred, and so small signal transistors have large stability factors.

#### Usage:

Due to the above inherent drawbacks, fixed bias is rarely used in linear circuits (i.e., those circuits which use the transistor as a current source). Instead, it is often used in circuits where transistor is used as a switch. However, one application of fixed bias is to achieve crude automatic gain control in the transistor by feeding the base resistor from a DC signal derived from the AC output of a later stage.

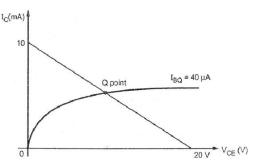

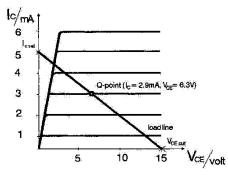

#### 2. Design the fixed bias circuit from the load line given in the figure. [CO1-H2]

Solution : From the load line we have,

$$V_{CC} = 20 V$$

$$\frac{V_{CC}}{R_C} = 10 \times 10^{-3} \qquad \therefore \quad R_C = \frac{20}{10 \times 10^{-3}} = 2 K$$

We have,

$$I_B = \frac{V_{CC} - V_{BE}}{R_B}$$

$$\therefore \qquad R_B = \frac{V_{CC} - V_{BE}}{I_B} = \frac{20 - 0.7 V}{40 \times 10^{-6}}$$

$$= 482.5 k\Omega$$

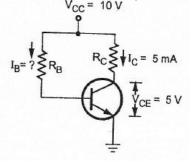

3. Design a fixed biased circuit using a silicon transistor having  $\beta$  value of 100. Vcc is 10 V and dc bias conditions are to be V<sub>CE</sub> = 5 V and I<sub>C</sub> = 5 mA, [CO1-H3]

Applying KVL to collector circuit,

$$V_{CC} - V_{CE} - I_C R_C = 0$$

$$\therefore R_C = \frac{V_{CC} - V_{CE}}{I_C} = \frac{10 - 5}{5 \text{ mA}} = 1 \text{ K}$$

$$I_B = \frac{I_C}{\beta} = \frac{5 \text{ mA}}{100} = 50 \text{ }\mu\text{A}$$

Applying KVL to base circuit,

$$V_{CC} - I_B R_B - V_{BE} = 0$$

$R_B = \frac{V_{CC} - V_{BE}}{I_B} = \frac{10 - 0.7}{50 \,\mu A} = 186 \,k\Omega$

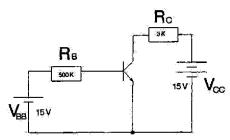

4. Calculate the operating point (Q-point)? [CO1-H1]

Base biased CE connection

$$I_{B} = \frac{V_{BB} - V_{BE}}{R_{B}} = \frac{14.3V}{500K\Omega} = 29\mu A$$

$$I_{C} = \beta_{dc} * I_{B} = 100 * 29\mu A = 2.9 \text{ mA}$$

$$V_{CE} = V_{CC} - (I_{C} * R_{C}) = 15V - (2.9 \text{ mA} * 3K\Omega) = 6.3V$$

By plotting  $I_C$  (2.9 mA) and  $V_{CE}$  (6.3V), we get the operation point ----> Q-point (quieSKPnt point).

Collector curve with load line and Q - point

#### S.K.P. Engineering College, Tiruvannamalai

#### 5. What are the Method of stabilizing the Q point [CO1-H1]

#### Stabilization technique:

It refers to the use of resistive biasing circuits which allow  $I_B$  to vary so as to keep  $I_C$  relatively constant with variations in  $I_{CO}$ ,  $\beta$  and  $V_{BE}$ .

#### **Compensation technique:**

It refers to the use of temperature sensitive devices such as diodes, transistors, thermistors which provide compensating voltage and current to maintain Q point stable.

#### **Stability Factors**

It is defined as the degree of change in operating point due to variation in temperature. There are three variables which are temperature dependent. Three stability factors are defined as follows,

i)

$$S = \frac{\partial I_C}{\partial I_{CO}}\Big|_{V_{BE,\beta} \text{ constant}}$$

or  $S = \frac{\Delta I_C}{\Delta I_{CO}}\Big|_{V_{BE,\beta} \text{ constant}}$

ii)  $S' = \frac{\partial I_C}{\partial V_{BE}}\Big|_{I_{CO,\beta} \text{ constant}}$  or  $S' = \frac{\Delta I_C}{\Delta V_{BE}}\Big|_{I_{CO,\beta} \text{ constant}}$

iii)  $S'' = \frac{\partial I_C}{\partial \beta}\Big|_{I_{CO,\gamma} \text{ be constant}}$  or  $S'' = \frac{\Delta I_C}{\Delta \beta}\Big|_{I_{CO,\gamma} \text{ be constant}}$

#### **Stability factor S:**

For a common emitter configuration collector current is given as,

or  $I_{C} = \beta I_{B} + I_{CEO}$  $I_{C} = \beta I_{B} + (1+\beta) I_{CBO}$

When  $I_{CBO}$  changes by  $\Delta I_{CBO}$ ,  $I_B$  changes by  $\partial I_B$  and  $I_C$  changes by  $\partial I_C$  equation becomes,

$$\partial I_{C} = \beta \partial I_{B} + (1+\beta) \partial I_{CBO}$$

$$\therefore \qquad 1 = \beta \frac{\partial I_{B}}{\partial I_{C}} + (1+\beta) \frac{\partial I_{CBO}}{\partial I_{C}}$$

$$\therefore \qquad 1 - \beta \frac{\partial I_{B}}{\partial I_{C}} = (1+\beta) \frac{\partial I_{CBO}}{\partial I_{C}}$$

$$\therefore \qquad \frac{\partial I_{CBO}}{\partial I_{C}} = \frac{1 - \beta (\partial I_{B} / \partial I_{C})}{1+\beta}$$

The above equation can be considered as a standard equation for the derivation of stability factors of other biasing circuits.

Stability factor S<sup>'</sup>:

$$S' = \frac{\partial I_C}{\partial V_{BE}} \Big|_{I_{CO},\beta \text{ constant}}$$

$I_C = \beta I_B + (\beta + 1) I_{CBO}$

$$S^{*} = \frac{\partial I_{C}}{\partial \beta} \Big|_{V_{BE}, I_{CO} \text{ constant}}$$

From equation (1.7.7) we have  $I_{C} = \frac{\beta V_{CC}}{R_{B}} - \frac{\beta V_{BE}}{R_{B}} + (\beta + 1) I_{CBO}$

$\frac{\partial I_{C}}{\partial \beta} = \left(\frac{V_{CC}}{R_{B}} - \frac{V_{BE}}{R_{B}}\right) + I_{CBO} = I_{B} + I_{CBO} = \frac{I_{C}}{\beta}$

$\frac{\partial I_{C}}{\partial \beta} = \frac{I_{C}}{\beta}$  Since  $I_{B} = \frac{I_{C}}{\beta}$  and  $I_{B} >> I_{CBO}$

#### **Relation between S and S":**

4

We know that S = 1+ $\beta$  and S" = I<sub>C</sub>/ $\beta$

Multiplying numerator and denominator by  $(1+\beta)$ , S" = I<sub>C</sub> $(1+\beta)$

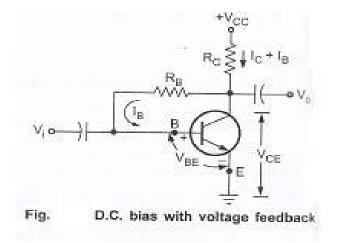

#### 6. Explain about Collector to Base Bias circuit [CO1-H2]

#### S.K.P. Engineering College, Tiruvannamalai

Figure shows the dc bias with voltage feedback. It is also called as collector to base bias circuit. It is an improvement over fixed bias method. In this, biasing resistor is connected between collector and base of the transistor to provide feedback path.

#### Circuit analysis: Base circuit:

Consider the base circuit and applying voltage law then we get,

$$\begin{split} V_{CC} &- (I_B + I_C) R_C - I_B R_B - V_{BE} &= 0 \\ V_{CC} &= (R_B + R_C) I_B + I_C R_C + V_{BE} \\ &= (R_B + R_C) I_B + \beta I_B R_C + V_{BE} \\ I_B &= \frac{V_{CC} - V_{BE}}{R_B + (I + \beta) R_C} \\ \end{split}$$

Only the difference between the equation for  $I_B$  and that obtained for fixed bias configuration is  $\beta R_{C_i}$  so the feedback path results in a reflection of the resistance  $R_C$  to the input circuit.

#### **Collector circuit:**

Applying KVL to the collector circuit,

$V_{CC} - (I_C + I_B) R_C - V_{CE} =$ 0  $V_{CE} = V_{CC} - (I_C + I_B) R_C$

If there is a change in  $\beta$  due to piece to piece variation between transistors or if there is a change in  $\beta$  and I <sub>CO</sub> due to the change in temperature. So collector current tends to increase. As a result, voltage drop across R<sub>C</sub> increases. Due to reduction in V<sub>CE</sub>, I<sub>B</sub> reduces. The result is that the circuit tends to maintain a stable value of collector current, keeping the Q point fixed.

In this circuit,  $R_B$  appears directly across input and output. A part of output is feedback to the input. And increase in collector current decreases the base current. So negative feedback exists in the circuit. It is also called as voltage feedback bias circuit.

#### Unit- II

#### **BJT Amplifiers**

#### Part- A

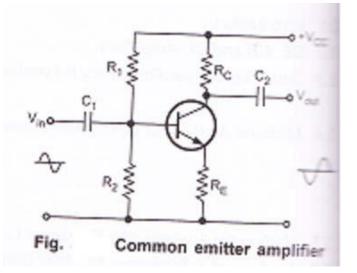

#### 1. What is an amplifier? [CO2-L1]

An amplifier is used to increase the signal level. It is used to get a larger signal output from a small signal input. Assume a sinusoidal signal at the input of the amplifier. At the output, signal must remain sinusoidal in waveform with frequency same as that of input. To make the transistor work as an amplifier, it is to be biased to operate in active region. It means base-emitter junction is forward biased and base-collector junction is reverse biased.

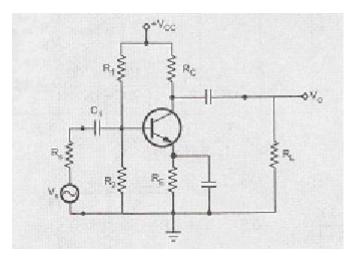

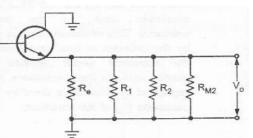

Let us consider the common emitter amplifier circuit using voltage divider bias.

#### 2. What are the main components present in the transistor circuits? [CO2-L1] 1. Biasing Circuit:

Resistors  $R_1$ ,  $R_2$  and  $R_E$  form the voltage divider biasing circuit for CE amplifier and it sets the proper operating point for CE amplifier.

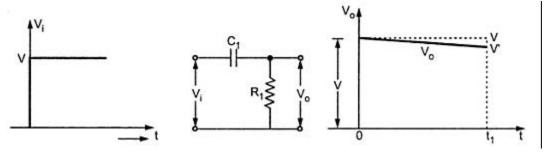

#### 2. Input Capacitor C<sub>1</sub>:

$C_1$  couples the signal to base of the transistor. It blocks any D.C. component present in the signal and passes only A.C. signal for amplification.

#### 3. Emitter Bypass Capacitor C<sub>E</sub>:

$C_E$  is connected in parallel with emitter resistance  $R_E$  to provide a low reactance path to the amplified A.C. This will reduce the output voltage and reducing the gain value.

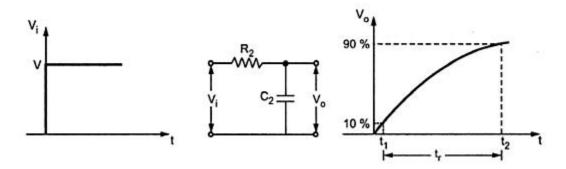

#### 4. Output Coupling Capacitor C<sub>2</sub>:

$C_2$  couples the output of the amplifier to the load or to the next stage of the amplifier. It blocks D.C. and passes only A.C. part of the amplified signal.

#### 3. what is mean by Phase reversal? [CO2-L1]

The phase relationship between the input and output voltages can be determined by considering the effect of positive and negative half cycle separately. The collector current is  $\beta$  times the base current, so the collector current will also increases. This increases the voltage drop across R<sub>c</sub>.

$$V_{\rm C} = V_{\rm CC} - I_{\rm C} R_{\rm C}$$

#### 4. What are the Benefits of h-parameters? [CO2-L1]

- Real numbers at audio frequencies

- o Easy to measure

- o Can be obtained from the transistor static characteristic curve

- Convenient to use in circuit analysis and design

- Most of the transistor manufacturers specify the h-parameters

#### 5. What are the methods to analyze the transistor circuit? [CO2-L2]

The analysis of transistor circuits for small signal behaviour can be made by following simple guidelines. These guidelines are,

- Draw the actual circuit diagram

- Replace coupling capacitors and emitter bypass capacitor by short circuit

- Replace D.C. source by a short circuit

- Mark the points B, E, C on the circuit diagram and locate these points as the start of the equivalent circuit

- Replace the transistor by its h-parameter model

#### 6. What are the two operating modes in the electronic circuits? [CO2-L2]

- Differential mode operation

- Common mode operation

#### 7. List the types of amplifier configurations? [CO2-L3]

- Dual input balanced output differential amplifier.

- Dual input, unbalanced output differential amplifier.

- Single input, balanced output differential amplifier.

- Single input, unbalanced output differential amplifier.

#### 8. How the impedance can be improved in the amplifiers? [CO2-L1]

The input impedance can be increased using two techniques :

- Using direct coupling (Darlington connection)

- Using Bootstrap technique

#### 9. What is the coupling schemes used in multistage amplifiers? [CO2-L2]

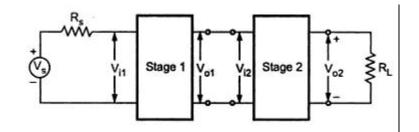

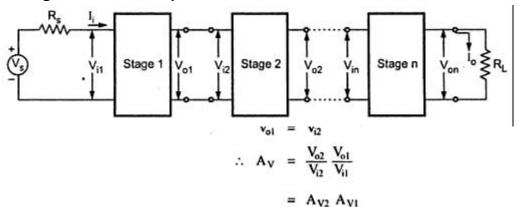

we need amplifier which can amplify a signal from a very weak source such as a microphone, to a level which is suitable for the operation of another transducer such as loudspeaker. This is achieved by cascading number of amplifier stages, known as multistage amplifier

#### 10. Define Common Mode Rejection Ratio (CMRR) [CO2-L2]

When the same voltage is applied to both the inputs, the differential amplifier is said to be operated in a common mode configuration. Many disturbance signals, noise signal appear as a common input signal to both the input terminals of the differential amplifier. Such a common signal should be rejected by the differential amplifier. The ability of a differential amplifier to reject a common mode signal is expressed by a ratio called common mode rejection ratio denoted as CMRR. It is defined as the ratio of the differential voltage gain  $A_d$  to common mode voltage gain  $A_C$

$$CMRR = \rho = \left| \frac{A_{d}}{A_{c}} \right|$$

$$CMRR \text{ in } dB = 20 \log \left| \frac{A_{d}}{A_{c}} \right| dB$$

#### 11. Define voltage & current gain of an emitter follower. [CO2-L1]

The current gain of the emitter follower is nearly 20 to 500 times greater compared with other both configurations. Also the voltage is moderate.

#### 12. What are the advantages of Representation of Gain in Decibels. [CO2-L2]

Logarithmic scale is preferred over linear scale to represent voltage and power gains because of the following reasons :

- In multistage amplifiers, it permits to add individual gains of the stages to calculate overall gain.

- It allows us to denote, both very small as well as very large quantities of linear, scale by considerably small figures.

For example, voltage gain of 0.0000001 can be represented as -140 dB and voltage gain of 1,00,000 can be represented as 100 dB.

• Many times output of the amplifier is fed to loudspeakers to produce sound which is received by the human ear. It is important to note that the ear responds to the sound intensities on a proportional or logarithmic scale rather than linear scale. Thus use of dB unit is more appropriate for representation of amplifier gains.

**12. What is the coupling schemes used in multistage amplifiers? (May,10) [CO2-L1]** In multistage amplifier, the output signal of preceding stage is to be coupled to the input circuit of succeeding stage. For this interstage coupling, different types of coupling elements can be employed.

These are : 1. RC coupling

- 2. Transformer coupling

- 3. Direct coupling

#### 13. Define Common Mode Rejection Ratio. (Nov, 09) [CO2-L2]

Common Mode Rejection Ratio is the figure of merit of a differential amplifier to reject common mode signal and is given by,

$$CMRR = \frac{\text{Gain of the amplifier for a difference mode input signal}}{\text{Gain of the amplifier for a common mode input signal}}$$

$$C = \left| \frac{A_d}{A_c} \right|$$

### 14. What does bootstrapping mean? Why bootstrapping is done in a buffer amplifier? (Nov, 10) [CO2-L3]

In the emitter follower amplifier  $A_V$  tends to unity. If a resistor is connected between input and output of the emitter follower, the change in the voltage at one end of the resistor changes the voltage at the other end of the resistor by same value. It is as if resistor is pulling itself up by its bootstraps. Such effect is known as *boot strapping*.

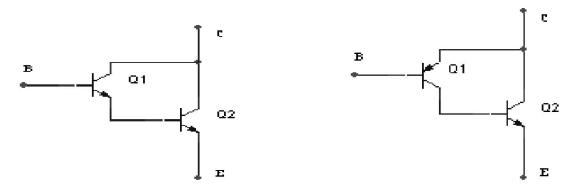

#### 15. Draw the Darlington emitter follower circuit. (May,14,13) [CO2-L3]

#### 16. How can a DC equivalent circuit of an amplifier be obtained? [CO2-L2]

The analysis of transistor circuits for small signal behavior can be made by following simple guidelines. These guidelines are,

- Draw the actual circuit diagram

- Replace coupling capacitors and emitter bypass capacitor by short circuit

- Replace D.C. source by a short circuit

- Mark the points B, E, C on the circuit diagram and locate these points as the start of the equivalent circuit

- Replace the transistor by its h-parameter model

#### 17. State Miller's Theorem. (May,15) [CO2-L1]

It states that the effect of resistance Z on the input circuit is a ratio of input voltage to the current which flows from the input to the output.

$$Z_1 = \frac{Z}{1-K}$$

It states that the effect of resistance Z on the output circuit is the ratio of output voltage to the current which flows from the output to input.

$$\mathsf{Z}_2 = \frac{\mathbb{Z} - \mathsf{K}}{\mathsf{K} - 1}$$

#### 18. Define i) Differential gain ii) Common mode gain [CO2-L1]

The gain with which differential amplifier amplifies the difference between two input signals is called differential gain of the differential amplifier denoted as A  $_{\rm D}$ . The gain with which it amplifies the common mode signal to produce the output is called common mode gain of the differential amplifier denoted as A  $_{\rm C}$ .

#### 19. What are practical limitations in selecting very high R E? [CO2-L2]

- Large R  $_{\rm E}$  needs higher biasing voltage to set the operating point of the transistors.

- This increases the overall chip area. Hence practically R  $_{\rm E}$  can not be selected very high.

#### 20. What are the limitations of h parameters? [CO2-L1]

The h parameters has the following limitations,

- The accurate calculation of h parameters is difficult.

- A transistor behaves as a two port network for small signals only, hence h parameters can be used to analyze only the small signal amplifiers.

#### 21. What are the advantages of Darlington amplifier? [CO2-L2]

A Darlington transistor connection provides a transistor having a very large current gain, typically a few thousand. The main features of the Darlington connection is that the composite transistor acts as a single unit with a current gain that is the product of current gains of the individual transistors.

βD= β1β2

$\beta D$  = Darlington connection current gain  $\beta 1$  and  $\beta 2$  – Current gain of the transistors 1 & 2 in the Darlington pair

#### 22. Methods of coupling multistage amplifiers. [CO2-L2]

- RC coupling

- o Transformer coupling

- o Direct coupling

#### 23. Features of differential amplifier, [CO2-L1]

- o High differential voltage gain

- Low common mode gain

- High CMRR

- o Two input terminals

- o High input impedance

- o Large bandwidth

- Low offset voltages and currents

- o Low output impedance

#### 24. List the configuration of differential amplifiers. [CO2-L3]

- o Dual input, balanced output differential amplifier

- o Dual input, unbalanced output differential amplifier

- o Single input, balanced output differential amplifier

- o Single input, unbalanced output differential amplifier

#### 25. State Bisection Theorem. (Nov, 12) [CO2-L1]

A particular network which has mirror symmetry with respect to an imaginary line. If the entire network is denoted as N then it can be divided into two half networks N/2 about the line of symmetry is called bisection theorem or Bartlett's bisection theorem.

#### 26. What are the other methods to improve CMRR without RE? [CO2-L1]

- o Constant current bias method

- Current mirror circuit.

#### 27. List the advantage of current mirror circuit? [CO2-L1]

- Provides very high emitter resistance RE.

- o Requires fewer components than the constant current bias.

- o Simple to design

- o Easy to fabricate.

- With properly matched transistors, collector current thermal stability is achieved.

28. Draw the small signal equivalent circuit of CE amplifier. [CO2-L3]

#### 28. Define Miller effect input capacitance.[Dec-2006, Dec2007, May-2008] [CO2-L2]

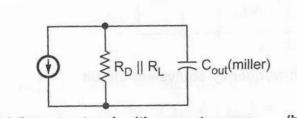

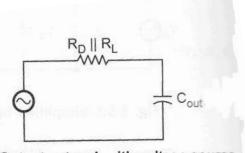

For any inverting amplifier, the input capacitance will be increased by a miller effect capacitance, sensitive to the gain of the amplifier and the inter electrode capacitance connected between the input and output terminals of the active device. CMi = (1 - AV) Cf CM0 = Cf Cf = Inter electrode capacitance between input and output.

#### PART B

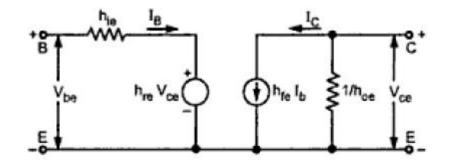

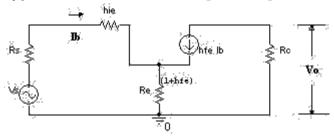

### 1. Explain about the Small Signal Low Frequency h-parameter Model of transistor amplifier. [CO2-H1]

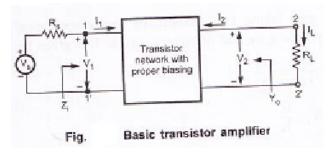

Let us consider the transistor amplifier as a block box.

Where,  $I_i$  – input current to the amplifier

- V<sub>i</sub> input voltage to the amplifier

- $I_o$  output current of the amplifier

- Vo output voltage of the amplifier

Input current is an independent variable. Input voltage and output current are dependent variables. Input current and output voltage are independent variables.

$V_i = f_1 (I_i, V_o)$  $I_o = f_2 (I_i, V_o)$

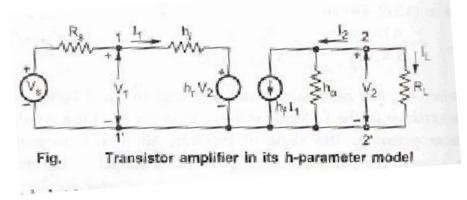

This can be written in the equation form as,

$$V_i = h_{11} I_i + h_{12} V_o$$

$$I_o = h_{21} I_i + h_{22} V_o \quad \text{eering Department} \qquad 24$$

III SEM

The above equation can also be written using alphabetic notations,

$$V_{i} = h_{i} \cdot I_{i} + h_{r} \cdot V_{o}$$

$$I_{o} = h_{f} \cdot I_{i} + h_{o} \cdot V_{o}$$

#### Definitions of h-parameter:

The parameters in the above equations are defined as follows

$$\begin{split} h_{11} &= \frac{V_i}{I_i} \Big|_{V_{0}=0} \\ h_{12} &= \frac{V_i}{V_o} \Big|_{I_{i}=0} \\ h_{21} &= \frac{I_o}{I_i} \Big|_{V_{0}=0} \\ h_{22} &= \frac{I_o}{V_o} \Big|_{I_{i}=0} \end{split}$$

$h_{11}$  – input resistance with output short-circuited in ohms

$h_{12}$  – fraction of output voltage at input with input open circuited, it is unitless  $h_{21}$  – forward current transfer ratio or current gain with output short circuited, it is unitless

h<sub>22</sub> - output admittance with input open circuited in mhos

#### Benefits of h-parameters:

- 1. Real numbers at audio frequencies

- 2. Easy to measure

- 3. Can be obtained from the transistor static characteristic curve

- 4. Convenient to use in circuit analysis and design

- 5. Most of the transistor manufacturers specify the h-parameters

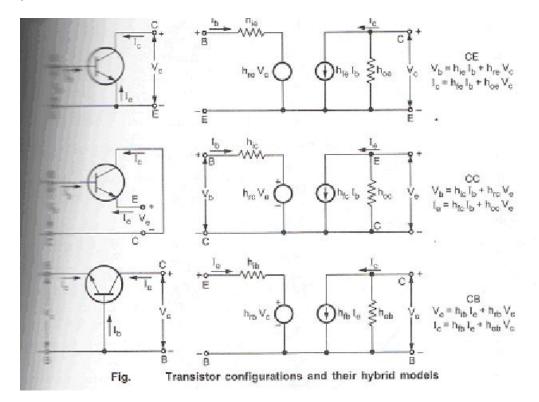

#### h-Parameters for all three configurations:

Transistor can be represented as two port network by making anyone terminal common between input and output. There are three possible configurations in which a transistor can be used, there is a change in terminal voltage and current for different transistor configurations. To designate the type of configuration another subscript is added to h-parameters.

$h_{ie} = h_{11e}$ - input resistance in CE configuration

$h_{fb} = h_{21b}$  – short circuit current gain in CB configuration

#### Table: Summarizes h-parameters for all three configurations

| Parameter                    | CB              | CE              | CC              |

|------------------------------|-----------------|-----------------|-----------------|

| lemen resistance             | h <sub>ib</sub> | h <sub>ie</sub> | h <sub>ic</sub> |

| Reverse voltage gain         | h <sub>rb</sub> | h <sub>re</sub> | h <sub>re</sub> |

| Howard transfer current gain | h <sub>fb</sub> | ħ fe            | h <sub>ft</sub> |

| Output admittance            | h <sub>ob</sub> | hoe             | hos             |

The basic circuit of hybrid model is same for all three configurations, only parameters are different.

The circuit and equations are valid for either NPN or PNP transistor and are independent of the type of load or method of biasing.

#### Determination of h-parameters from characteristics:

Consider CE configuration, its functional relationship can be defined from the following equations:

$$V_{be} = f_1 (I_b, V_{ce})$$

$$I_c = f_2 (I_b, V_{ce})$$

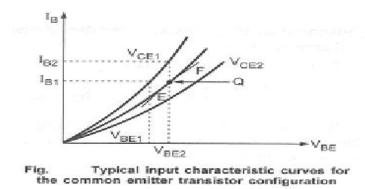

The input characteristic curve gives the relationship between input voltage  $V_{BE}$  and input current I <sub>B</sub> for different values of output voltage  $V_{CE}$ . The following figure shows the typical input characteristic curve for CE configuration.

Determination of  $h_{ie}$  and  $h_{re}$  from characteristic curve: Parameter  $h_{ie}$ :

$$h_{ie} = \frac{\Delta V_{BE}}{\Delta I_B} \bigg|_{V_{CE \text{ constant}}} = \frac{V_{BE2} - V_{BE1}}{I_{B2} - I_{B1}}$$

Parameter h<sub>re</sub>:

$$\mathbf{h}_{re} = \frac{\Delta |\mathbf{V}_{BE}|}{\Delta |\mathbf{V}_{CE}|_{IBconstant}} = \frac{\mathbf{V}_{BE2} - \mathbf{V}_{BE1}}{\mathbf{V}_{CE2} - \mathbf{V}_{CE1}}$$

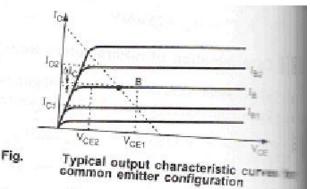

The output characteristic curve gives the relationship between output current  $I_C$  and output voltage  $V_{CE}$  for different values of input current  $I_B$ .

Electronics and Comm

Electronic Circuits I

#### Determination of $h_{fe}$ and $h_{oe}$ from output characteristic curve:

Parameter h<sub>fe</sub>:

$$h_{fe} = \frac{\Delta I_C}{\Delta I_B} \bigg|_{V_{CE \text{ constant}}} \approx \frac{I_{C2} - I_{C1}}{I_{B2} - I_{B1}}$$

Parameter hoe:

$$h_{oe} = \frac{\Delta I_{C}}{\Delta V_{C}} \bigg|_{I_{Bconstant}} = \frac{I_{C2} - I_{C1}}{V_{CE2} - V_{CE1}}$$

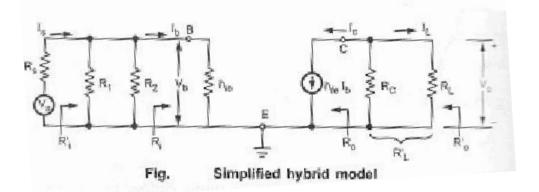

2. Detail about Mid band analysis of BJT Single Stage Amplifiers [CO2-H2] Consider the basic amplifier circuit. To form a transistor amplifier only is is necessary to connect an external load and signal source along with proper biasing.

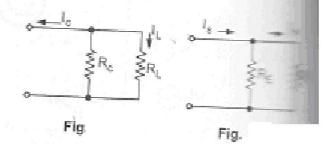

We can replace the transistor circuit as shown in the following figure.

Let us analyze the hybrid model to find current gain, input resistance, voltage gain and output resistance.

#### Current gain (A<sub>i</sub>):

It is defined as the ratio of output to input current. It is given by,

Electronics and Communication Engineering De<sub>1</sub>

$$A_i = \frac{I_L}{I_1} = -\frac{I_2}{I_1}$$

Electronic Circuits I

Here  $I_L$  and  $I_2$  are equal in magnitude but opposite in sign.  $I_L = -I_2$

From above circuit,

$$I_2 = h_f I_1 + h_0 V_2$$

Substituting  $V_2 = -I_2R_L$  in the equation, then equation become,

$$I_{2} = h_{f} I_{1} + h_{o} (-I_{2} R_{L})$$

$$I_{2} + h_{o} I_{2} R_{L} = h_{f} I_{1}$$

$$(I + h_{o} R_{L}) I_{2} = h_{f} I_{1}$$

$$\frac{I_{2}}{I_{1}} = \frac{h_{f}}{1 + h_{o} R_{L}}$$

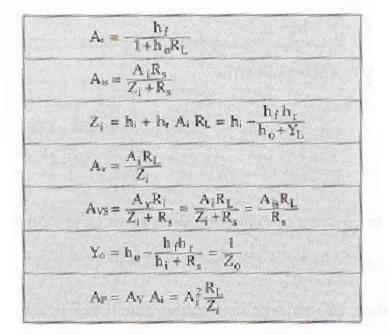

$$A_{i} = -\frac{I_{2}}{I_{i}} = \frac{-h_{f}}{1 + h_{o} R_{L}}$$

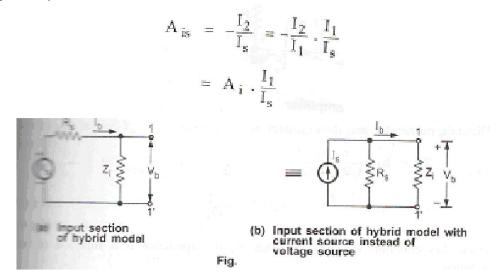

Current gain (A<sub>IS</sub>):

It is given by,

From above figure, using current divider rule,

$$I_1 = \frac{I_s R_s}{Z_i + R_s}$$

$$\frac{I_i}{I_s} = \frac{R_s}{Z_i + R_s}$$

$$A_{is} = \frac{A_i R_s}{Z_i + R_s}$$

#### Input Impedance (Z<sub>i</sub>):

$R_i$  is the input resistance looking into the amplifier input terminals (1, 1'). It is given by,

$$R_i = \frac{V_1}{I_1}$$

From the input circuit,

$$V_{1} = h_{i} I_{1} + h_{r} V_{2}$$

$$Z_{i} = \frac{V_{1}}{I_{1}} = \frac{h_{i} I_{1} + h_{r} V_{2}}{I_{1}}$$

$$Z_{i} = h_{i} + h_{r} \frac{V_{2}}{I_{1}}$$

Substituting  $V_2 = -I_2R_L = A_i I_1 R_L$  in the above equation,

$$Z_i = h_i + \frac{h_r A_i I_1 R_L}{I_1} = h_i + h_r A_i R_L$$

Substituting

$$A_{i} = -\frac{h_{f}}{1 + h_{o} R_{L}}$$

Then we get,

$$Z_i = h_i - \frac{h_r h_f R_L}{1 + h_o R_L}$$

Dividing numerator and denominator by R<sub>L</sub> we get,

$$Z_{i} = h_{i} - \frac{h_{r} h_{f}}{1/R_{L} + h_{o}}$$

$$Z_{i} = h_{i} - \frac{h_{r} h_{f}}{Y_{L} + h_{o}} \text{ where } Y_{L} = \frac{1}{R_{L}}.$$

From this equation, note that the input impedance is a function offload impedance. Voltage gain  $(A_v)$ :

It is the ratio of output voltage to input voltage. It is given by,

$$A_{v} = \frac{V_2}{V_1}$$

By substituting  $V_2 = -I_2R_L = A_i I_1 R_L$

$$A_{V} = \frac{A_{i} I_{I} R_{L}}{V_{i}} = \frac{A_{i} R_{L}}{Z_{i}}$$

$$\frac{I_{I}}{V_{i}} = \frac{1}{Z_{i}}$$

30

Electronics and Communication Engineering Department

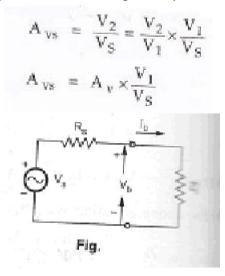

#### Voltage gain (A<sub>vs</sub>):

It is voltage gain including the source. It is given by,

From above figure, applying potential divider rule, then we get,

$$V_1 = \frac{Z_i}{R_s + Z_i} V_s$$

$$\frac{V_1}{V_s} = \frac{Z_i}{R_s + Z_i}$$

Substituting the value of  $V_1/V_s$  in the equation of

$$A_{vs} = A_v \times \frac{V_1}{V_s}$$

We get,

$$A_{vs} = A_v \cdot \frac{Z_i}{R_s + Z_i}$$

$$= \frac{A_i R_L}{R_s + R_i} \quad \forall \quad A_v = \frac{A_i R_L}{Z_i}$$

#### Output Admittance (Y<sub>o</sub>):

It is the ratio of output current to output voltage. It is given by,

$$Y_{\oplus} = \frac{I_2}{V_2}$$

with  $V_s = 0$

From equation,

$I_2 = h_f I_1 + h_o V_2$ Electronics and Communication Engineering Department 31

Electronic Circuits I

Dividing above equation by  $V_2$ , We get, From transistor amplifier in h-parameter model circuit, with  $V_s = 0$ ,

$$\frac{I_2}{V_2} = \frac{h_f I_1}{V_2} + h_o$$

$$Y_o = h_f \frac{I_1}{V_2} + h_o$$

$R_{s}I_{1} + h_{i}I_{1} + h_{r}V_{2} = 0 (R_{s} + h_{i}) I_{1} = -h_{r}$   $V_{2}$   $\frac{I_{1}}{V_{2}} = \frac{-h_{r}}{R_{s} + h_{i}}$

Substituting the value of  $I_1/V_2$  from above equation in the equation of  $Y_o$ , We obtain,

$$Y_o = h_o - \frac{h_f h_r}{h_i + R_s}$$

From this equation, note that the output admittance is a function of source resistance.

#### Power gain (Ap):

It is the ratio of average power delivered to the load to the input power. Output power is given as,

$$P_2 = V_2 I_L = -V_2 I_2$$

Since the input power is  $P_1 = V_1 I_1$

The operating power gain  $A_p$  of the transistor is given as,

$$A_{P} = \frac{P_{2}}{P_{1}} = -\frac{V_{2}I_{2}}{V_{1}I_{1}} = A_{V}A_{1} = A_{1}^{2}\frac{R_{L}}{Z_{1}} \quad \forall A_{V} = \frac{A_{1}R_{L}}{Z_{1}}$$

#### Relation between $A_{vs}$ and $A_{IS}$ :

From equation,

$$A_{vs} = \frac{A_i R_L}{R_s + R_i} \quad \because \quad A_v = \frac{A_i R_L}{Z_i} \quad \text{and} \quad A_{is} = \frac{A_i R_s}{Z_i + R_s}$$

We have,

S.K.P. Engineering College, Tiruvannamalai

$$A_{vs} = \frac{A_i R_L}{Z_i + R_s} \qquad A_{is} = \frac{A_j R_s}{Z_i + R_s}$$

Taking ratio of above two equations we get,

$$\frac{A_{vs}}{A_{is}} = \frac{R_L}{R_s}$$

$$A_{vs} = A_{is} \cdot \frac{R_L}{R_s}$$

#### Table: Summarizes small signal analysis of a transistor amplifier

#### Method for analysis of a transistor circuit:

The analysis of transistor circuits for small signal behaviour can be made by following simple guidelines. These guidelines are,

- Draw the actual circuit diagram

- Replace coupling capacitors and emitter bypass capacitor by short circuit

- Replace D.C. source by a short circuit

- Mark the points B, E, C on the circuit diagram and locate these points as the start of the equivalent circuit

- Replace the transistor by its h-parameter model

Electronic Circuits I

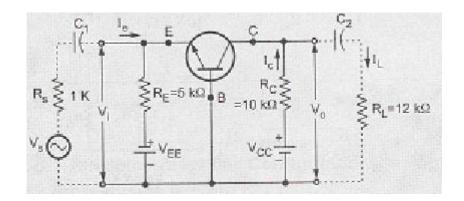

3. For the common base circuit shown in figure, transistor parameters are  $h_{ib} = 22\Omega$ ,  $h_{fb} = -0.98$ ,  $h_{ob} = 0.49\mu$ A/V,  $h_{rb} = 2.9*10^{-4}$ . Calculate the values of input resistance, output resistance, current gain and voltage gain for the given circuit. [CO2-H2]

#### Solution:

Change the given figure into h-parameter equivalent model.

a) Current gain

$$(A_{i}) = -\frac{h_{fb}}{1 + h_{ob}R'_{L}}$$

$$= \frac{-(-0.98)}{1 + 0.49 \times 10^{-6} \times 5.45 \text{ K}} = 0.977$$

b) Input Resistance

34

c) Voltage gain  $(A_v) = \frac{A_i R'_L}{R_i} = \frac{(0.977) \times (5.45 \text{ K})}{23.54} = 226$

d) Overall voltage gain

$$A_{vs} = \frac{V_o}{V_s} = \frac{V_o}{V_e} \times \frac{V_e}{V_s} \text{ where } \frac{V_o}{V_e} = A_v \frac{V_e}{V_s} = \frac{R'_i}{R'_i + R_s}$$

$$A_{vs} = A_v \frac{R'_i}{R'_i + R_s} = 226 \times \frac{23.43}{20.36 + 1 \text{ K}} = 5.174$$

e) Overall current gain

$$A_{i} = \frac{I_{L}}{I_{s}} = \frac{I_{L}}{I_{c}} \times \frac{I_{c}}{I_{e}} \times \frac{I_{e}}{I_{s}}$$

$$\frac{I_{L}}{I_{c}} = -\frac{R_{C}}{R_{C} + R_{L}} = -\frac{10 \text{ K}}{10 \text{ K} + 12 \text{ K}} = -0.454$$

$$\frac{I_c}{I_e} = -A_i = -0.977$$

$$\frac{I_e}{I_s} = \frac{R_E}{R_E + R_i} = \frac{5 \text{ K}}{5 \text{ K} + 23.54} = 0.995$$

$$\therefore A_{i(\text{for circuit})} = (-0.454) \times (-0.977) \times 0.996 = 0.441$$

#### f) Output Resistance

$$\begin{aligned} (R_{0}) &= \frac{1}{h_{0b} - \frac{h_{fb}h_{rb}}{h_{ib} + R'_{s}}} \\ &= \frac{1}{\frac{1}{0.49 \times 10^{-6} - \left(\frac{-0.98 \times 2.9 \times 10^{-4}}{22 + 833.33}\right)}} = 1.21 \text{ M}\Omega \end{aligned}$$

$R_{o}^{'} = R_{o} \parallel R_{L}' = 1.21M \parallel 5.45K = 5.425K\Omega$

**Problem 2:** Consider a single stage CE amplifier with  $R_s = 1K\Omega$ ,  $R_L = 1.2K\Omega$ . Calculate  $A_i$ ,  $R_i$ ,

$A_v$ ,  $A_{is}$ , power gain and  $R_o$  if  $h_{ie} = 1.1k$ ,  $h_{re} = 2.5*10^{-4}$ ,  $h_{fe} = 50$  and  $h_{oe} = 25\mu A/V$ . [CO2-H2]

Solution:

Ai =

$$\frac{-h_{fe}}{1+h_{oe} R_L} = \frac{-50}{1+25 \times 10^{-6} \times 1.2 \times 10^3} = -48.54$$

$$\mathsf{R}_{i} = \frac{\mathsf{h}_{ie} + \mathsf{h}_{re} \,\mathsf{A}_{i} \,\mathsf{R}_{L}}{\mathsf{h}_{re} = 1100 - 2.5 \times 10^{-4} \times 48.54 \times 1200} = 1085.44 \,\Omega$$

$$A_{v} = \frac{A_{i} R_{L}}{R_{i}} = \frac{-48.54 \times 1200}{1085.44} = -53.663$$

$$A_{vs} = \frac{A_v R_i}{R_i + R_s} = -\frac{53.663 \times 1085.44}{1085.44 + 1000} = -27.93$$

$$\frac{A_{1}R_{s}}{R_{1} + R_{s}} = -\frac{48.54 \times 1000}{1085.44 + 1000} = -23.28$$

A<sub>is</sub> =

$$h_{ce} - \frac{h_{fe} h_{re}}{h_{ie} + R_s} = 25 \times 10^{-6} - \frac{50 \times 2.5 \times 10^{-4}}{1100 + 1000} = 19.0 \ \mu A/V$$

$$Y_o =$$

$$\frac{1}{Y_o} = \frac{1}{19 \times 10^{-6}} = 52.6 \text{ K}$$

#### Problem 3:

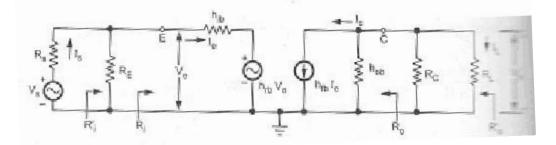

Consider a single stage CE amplifier with  $R_s = 1k$ ,  $R_1 = 50k$ ,  $R_2 = 2k$ ,  $R_c = 2k$ ,  $R_L = 2K$ ,  $h_{ie} = 1.1k$ ,  $h_{oe} = 25\mu A/V$ ,  $h_{fe} = 50$  and  $h_{re} = 2.5*10^{-4}$  as shown in the figure. Find Ai, R<sub>i</sub>, A<sub>v</sub>, A<sub>i</sub>, A<sub>vs</sub> and R<sub>o</sub>. [**CO2-H3**]

#### Solution:

Since  $h_{oe} R_{L}^{'} = 25*10^{-6*}(2K \parallel 2K) = 0.25$ , which is less than 0.1, so use approximate analysis.

Consider the simplified hybrid model for the given circuit.

a) Current gain

$$(A_v) = \frac{A_i R_L}{R_i} = \frac{-50 \times (2K)|2K}{1.1K} = -45.45$$

#### b) Input Impedance

$$(R_i) = h_{ie} = 1.1 \ K$$

Electronics and Con  $\mathbb{R}'_i = \mathbb{h}_{ie} \parallel \mathbb{R}_1 \parallel \mathbb{R}_2 = 1.1 \text{ K} \parallel 50 \text{ K} \parallel 2 \text{ K} = 700 \text{ G}$

Electronic Circuits I

$$(A_i) \ = \ - h_{fe} = - \ 50$$

c) Output Impedance

$$R_{0} = \frac{1}{Y_{0}} = \infty$$

ť

d) Overall voltage gain

$$R'_{o} = R_{o} \parallel R'_{L} = \infty \parallel 2 \text{ K} \parallel 2 \text{ K} = 1 \text{ K}$$

$$(A_{vs}) = \frac{V_{o}}{V_{s}} = \frac{V_{o}}{V_{b}} \times \frac{V_{b}}{V_{s}}$$

$$R'_{vs} = \frac{A_{v} R'_{i}}{R'_{i} + R_{s}} = \frac{-45.45 \times 700}{700 + 1 \text{ K}} = -18.71$$

e) Overall current gain

$$A_{i} = \frac{I_{L}}{I_{s}} = \frac{I_{L}}{I_{c}} \times \frac{I_{c}}{I_{b}} \times \frac{I_{b}}{I_{s}}$$

$$\stackrel{\bullet}{\longrightarrow} \frac{I_{c}}{Fig.} \xrightarrow{Fig.} \stackrel{I_{c}}{\longrightarrow} \frac{I_{s}}{Fig.}$$

$$\stackrel{I_{L}}{\longrightarrow} \frac{I_{L}}{I_{c}} = -\frac{R_{c}}{R_{c} + R_{L}} = \frac{-1K}{1K + 1K} = -0.5$$

$$\frac{I_{c}}{I_{b}} = h_{fe} = 50$$

| Sr.No. | Characteristic                   | Common Base                                 | Common Emitter                 | Common Collector               |

|--------|----------------------------------|---------------------------------------------|--------------------------------|--------------------------------|

| 1.     | Input resistance                 | Very low (20 Ω)                             | Low $(1 \ k\Omega)$            | High (500 kΩ)                  |

| 2.     | Output resistance                | Very high (1 MΩ)                            | High (40 kΩ)                   | Low (50 Ω)                     |

| 3.     | Input current                    | IE                                          | IB                             | IB                             |

| 4.     | Output current                   | I <sub>C</sub>                              | 1 <sub>C</sub>                 | IE                             |

| 5.     | Input voltage<br>applied between | Emitter and Base                            | Base and Emitter               | Base and Collector             |

| 6.     | Output voltage<br>taken between  | Collector and Base                          | Collector and<br>Emitter       | Emitter and Collector          |

| 7.     | Current<br>amplification factor  | $\alpha = \frac{I_C}{I_E}$                  | $\beta = \frac{I_C}{I_B}$      | $\gamma = \frac{I_{E}}{I_{B}}$ |

| 8.     | Current gain                     | Less than unity                             | High<br>(20 to few hundreds)   | High<br>(20 to few hundreds)   |

| 9.     | Voltage gain                     | Medium                                      | Medium                         | Low                            |

| 10.    | Applications                     | As a input stage of<br>multistage amplifier | For audio signal amplification | For impedance matching         |

## **Comparison of Transistor Configurations:**

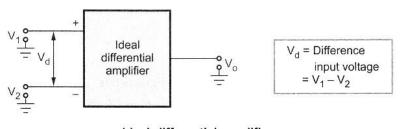

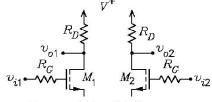

## 13. Explain briefly about differential amplifier and derive its expressions. [CO2-H2]

A device which accepts an input signal and produces an output signal proportional to the input, is called an amplifier. An amplifier which amplifies the difference between the two input signals is called differential amplifier. The differential amplifier configuration is used in variety of analog circuits. The differential amplifier is an essential and basic building block in modern IC amplifier .The Integrated Circuit (IC)technology is well known now a days, due to which the design of complex circuits become very simple. The IC version of operational amplifier is inexpensive, takes up less space and consumes less power. The. differential amplifier is the basic building block of such IC operational amplifier.

#### **Basics of Differential Amplifier**

The Differential Amplifier amplifies the difference between two input voltage signal. Hence it is also called as difference amplifier.

Consider an ideal differential amplifier shown in the Fig. A

Fig. Ideal differential amplifier

$V_1$  and  $V_2$  are the two input signals while Vo is the output. Each signal is measured with respect to the ground. In an ideal differential amplifier, the output voltage Vo is proportional to the difference between the two input signals. Hence

Т

we can write,

$$V_o \propto (V_1 - V_2) | \dots (-1) |$$

Differential Gain A<sub>d</sub>

From Equation 1 we can write,

$$\therefore \qquad V_o = A_d (V_1 - V_2) \qquad \dots (\cdot 2)$$

where  $A_D$  is the constant of proportionality. The  $A_D$  is the gain with which differential amplifier amplifies the difference between two input signals. Thus it is called differential gain of the differential amplifier.

Thus, Ad = Differential gain. The difference between the two inputs  $(V_1 - V_2)$  is generally called difference voltage and denoted as Vd.

$$V_o = A_d V_d$$

...(3)

Hence the differential gain can be expressed as,

$$A_d = \frac{V_o}{V_d} \dots (4)$$

Generally the differential gain is expressed in its decibel (dB) value as,

$$A_d = 20 \log_{10} (A_d) \text{ in } dB \dots (5)$$

## Common Mode Gain Ac

If we apply two input voltages which are equal in all the respects to the differential amplifier i.e. V1 = Vz then ideally the output voltage  $Vo = (V_1 - V_2) A_d$ , must be zero.But the output voltage of the practical differential amplifier not only depends on the difference voltage but also depends on the average common level of the two inputs.Such an average level of the two input signals is called common mode signal denoted as  $V_c$

$$V_c = \frac{V_1 + V_2}{2} \dots (6)$$

Practically, the differential amplifier produces the output voltage proportional to such common mode signal, also. The gain with which it amplifies the common mode signal to produce the output is called common mode gain of the differential amplifier  $A_{C.\lambda}$

Electronics and Communication Engineering Department

$$V_o = A_c V_c |..(7)$$

Thus there exists some finite output for V1 = V2 due to such common mode gain  $A_{C_i}$  in case of practical differential amplifiers.

So the total output of any differential amplifier can be expressed as,

$$V_{o} = A_{d} V_{d} + A_{c} V_{c} |..(8)$$

For an ideal differential amplifier, the differential gain  $A_d$ , must be infinite while the common mode gain must be zero.

But due to mismatch in the internal circuitry, there is some output available for  $V_1 = V_2$  and gain  $A_C$  is not practically zero. The value of such common mode gain  $A_C$  very small while the value of the differential gain  $A_d$  is always very large.

#### **Common Mode Rejection Ratio (CMRR)**

When the same voltage is applied to both the inputs, the differential amplifier is said to be operated in a common mode configuration. Many disturbance signals, noise signal appear as a common input signal to both the input terminals of the differential amplifier. Such a common signal should be rejected by the differential amplifier. The ability of a differential amplifier to reject a common mode signal is expressed by a ratio called common mode rejection ratio denoted as CMRR. It is defined as the ratio of the differential voltage gain  $A_d$  to common mode voltage gain  $A_c$

$$CMRR = \rho = \frac{|A_d|}{|A_c|} \quad \dots (9)$$

CMRR in dB = 20 log  $\left| \frac{A_d}{A_c} \right| dB$  .....(10)

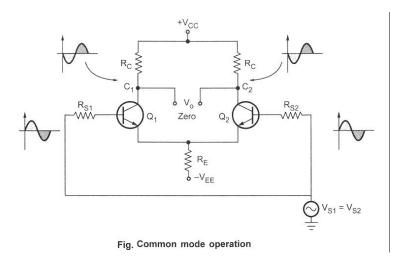

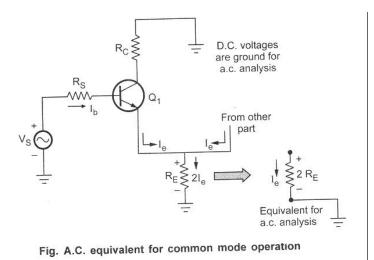

## 14. Discuss about Common Mode Operation. [CO2-H2]

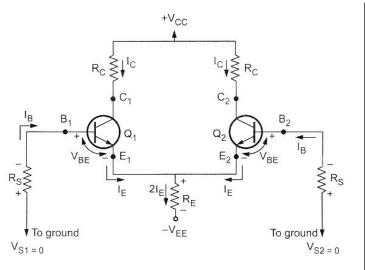

In this mode, the signals applied to the base of Q1 and Q2 are derived from the same source. So the two signals are equal in magnitude as well as in phase. The circuit diagram is shown in the Fig.

In phase signal voltages at the bases of Q1 and Q2 causes in phase signal voltages to appear across R  $_{E}$ , which add together. Hence R  $_{E}$  carries a signal current and provides a negative feedback. This feedback reduces the common mode gain of differential amplifier.

While the two signals causes in phase signal voltages of equal magnitude to appear across the two collectors of Q<sub>1</sub> and Q2. Now the output voltage is the difference between the two collector voltages, which are equal and also same in phase, Eg. (20) - (20) = 0. Thus the difference output Vo is almost zero, negligibly small. ideally it should be zero.

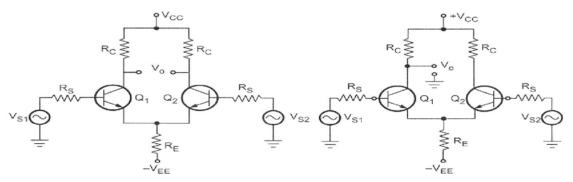

#### **Configurations of Differential Amplifier**

The differential amplifier, in the difference amplifier stage in the op-amp, can be used in four configurations :

- Dual input balanced output differential amplifier.

- Dual input, unbalanced output differential amplifier.

- Single input, balanced output differential amplifier.

- Single input, unbalanced output differential amplifier.

The differential amplifier uses two transistors in common emitter configuration. If output is taken between the two collectors it is called balanced output or double ended output. While if the output is taken between one collector with respect to ground it is called unbalanced output or single ended output. If the signal is given to both the input terminals it is called dual input, while if the signal is given to only one input terminal and other terminal is grounded it is called single input or single ended input. Out of these four configurations the dual input, balanced output is the basic differential amplifier configuration. This is shown in the Fig. (a). The dual input, unbalanced output differential amplifier is shown in the Fig. (b). The single input, balanced output differential amplifier is shown in the Fig. (c) and the single input, unbalanced output differential amplifier is shown in the Fig. (d).

(a) Dual input balanced output

(c) Single input balanced output

(b) Dual input unbalanced output

(d) Single input unbalanced output

#### **D.C. Analysis of Differential Amplifier**

The d.c. analysis means to obtain the operating point values i.e. I  $_{C}q$  and V  $_{CEQ}$  for the transistors used. The supply voltages are d.c. while the input signals are a.c., so d.c equivalent circuit can be obtained simply by reducing the input a.c. signals to zero. The d.c. equivalent circuit thus obtained is shown in the Fig.. Assuming Rs  $_{1} = R_{S2}$ , the source resistance is simply denoted by

Fig. D.C. equivalent circuit

The transistors Q1 and Q  $_2$  are matched transistors and hence for such a matched pair we can assume :

i) Both the transistors have the same characteristics. ii) R  $_{E1}$  = R  $_{E2}$  hence R  $_{E}$  = R  $_{E1}$  II R  $_{E2}$ .

iii) R  $_{C1}$  = R c  $_2$  hence denoted as R  $_C$ .

iv) IV  $_{CC}I = IV _{EE}I$  and both are measured with respect to ground.

As the two transistors are matched and circuit is symmetrical, it is enough to find out operating point I  $_{CQ}$  and V  $_{CEQ}$ , for any one of the two transistors. The same is applicable for the other transistor.

Apply-g KVL to base-emitter loop of the transistor Q1,

$$-I_BR_S - V_{BE} - 2I_ER_E + V_{EE} = 0$$

....(1)

$$I_{\rm C} = \beta I_{\rm B} \text{ and } I_{\rm C} \cong I_{\rm E}$$

$I_{\rm B} = \frac{I_{\rm E}}{\beta} \qquad \dots (2)$

Substituting in equation (1), we get

$$\frac{-I_{\rm E} R_{\rm S}}{\beta} - V_{\rm BE} - 2I_{\rm E} R_{\rm E} + V_{\rm EE} = 0$$

....(3)

$$I_{E} \left[ \frac{-R_{S}}{\beta} - 2R_{E} \right] + V_{EE} - V_{BE} = 0 \qquad \dots (4)$$

$$I_{E} = \frac{V_{EE} - V_{BE}}{\frac{R_{S}}{\beta} + 2R_{E}} \qquad \dots (.5)$$

$$V_{BE} = 0.6 \text{ to } 0.7 \text{ V for silicon}$$

$$= 0.2 \text{ V for germanium transistors.}$$

1

In practice, generally  $~\frac{R_{S}}{\beta} < < 2$  R  $_{E}$

$$I_{\rm E} = \frac{V_{\rm EE} - V_{\rm BE}}{2R_{\rm E}} \dots (6)$$

Now let us determine  $V_{CE}$ . As  $I_E$  is known and  $I_E \cong I_{C'}$  we can determine the collector voltage of  $Q_1$  as

$$V_{\rm C} = V_{\rm CC} - I_{\rm C} R_{\rm C} \qquad \dots (7)$$

Neglecting the drop across  $R_S$ , we can say that the voltage at the emitter of  $Q_1$  is approximately equal to  $-V_{BE}$ . Hence the collector to emitter voltage is

$$V_{CE} = V_{C} - V_{E} = (V_{CC} - I_{C}R_{C}) - (-V_{BE})$$

$$V_{CE} = V_{CC} + V_{BE} - I_{C}R_{C}$$

...(8)

Hence  $I_E = I_C = I_{CQ}$  while  $V_{CE} = V_{CEQ}$  for given values of  $V_{CC}$  and  $V_{EE}$ .

Thus for both the transistors, we can determine operating point values, using equations (6) and (8) With the same biasing arrangement, the d.c. analysis remains same for all the four possible configurations of differential amplifier.

$$I_E = \frac{V_{EE} - V_{BE}}{\frac{R_s}{\beta} + 2R_E} \approx \frac{V_{EE} - V_{BE}}{2R_E} \approx I_{CQ}$$

$$V_{CEQ} = V_{CC} + V_{BE} - I_{CQ}R_C$$

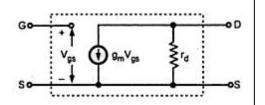

## 15. Important aspects of A.C. Analysis of Differential Amplifier using h-Parameters [CO2-H2]

In the a.c. analysis, we will calculate the differential gain A  $_{d}$ , common mode gain A  $_{C}$ , input resistance Ri and the output resistance R  $_{0}$  of the differential amplifier circuit, using the h-parameters.

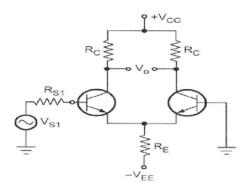

#### 1. Differential Gain (A d)

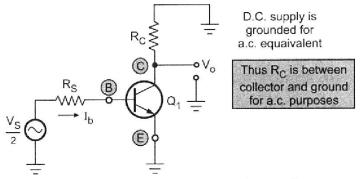

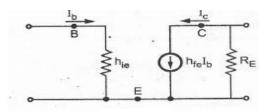

For the differential gain calculation, the two input signals must be different from each other. Let the two a.c. input signals be equal in magnitude but having 180" phase difference in between them. The magnitude of each a.c. input voltage V  $_{S1}$  and V  $_{S2}$  beVs /2. The two a.c. emitter currents I  $e_1$  and I  $e_2$  are equal in magnitude and 180' out of phase. Hence they cancel each other to get resultant a.c. current through the emitter as zero. For the a.c. purposes emitter terminal can be grounded. The a.c. small signal differential amplifier circuit with grounded emitter terminal is shown in the Fig1 As the two transistors are matched, the a.c. equivalent circuit for the other transistor is identical to the one shown in the Fig.1.

45

Thus the circuit can be analyzed by considering only one transistor. This is called as half circuit concept of analysis. The approximate hybrid model for the above circuit can be shown as in the Fig.2, neglecting ho<sub>e</sub>,

Fig.1 A.C. equivalent for differential operation

Fig.2 Approximate hybrid model

Applying KVL to the input loop,

$$-I_{b}R_{S} - I_{b}h_{ie} + \frac{V_{S}}{2} = 0 \qquad \dots(1)$$

$$-I_{b}(R_{S} + h_{ie}) = -\frac{V_{S}}{2}$$

$$I_{b} = \frac{V_{S}}{2(R_{S} + h_{ie})} \qquad \dots(2)$$

Applying KVL to the output loop,

$$V_o = -h_{fe} I_b R_C$$

...(3)

Substituting equation (2) in equation (3),

$$V_{o} = -h_{fe} R_{C} \frac{V_{S}}{2(R_{S} + h_{ie})}$$

$$\frac{V_{o}}{V_{S}} = \frac{-h_{fe} R_{C}}{2(R_{S} + h_{ie})} \dots 4^{3}$$

1

The negative sign indicates the phase difference between input and output. Now two input signal magnitudes are  $V_S$  /2 but they are opposite in polarity, as 180" out of phase.

$$V_{d} = V_{1} - V_{2} = \frac{V_{S}}{2} - \left(-\frac{V_{S}}{2}\right) = V_{S}$$

The **magnitude** of the differential gain  $A_{d}$  is

$$A_{d} = \frac{V_{o}}{V_{S}} = \frac{h_{fe} R_{C}}{2 (R_{S} + h_{ie})}$$

(For unbalanced output) ...(5)

where  $V_{S}$  = Differential input

#### the expression for A $_{\rm d}$ with balanced output changes as

$$A_{d} = 2 \times \frac{h_{fe} R_{C}}{2(R_{S} + h_{ie})}$$

$$A_{d} = \frac{h_{fe} R_{C}}{(R_{S} + h_{ie})} \text{ (magnitude)} \dots 6$$

This is the differential gain for balanced output dual input differential amplifier circuit.

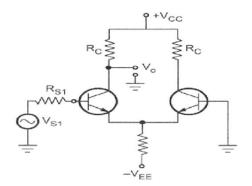

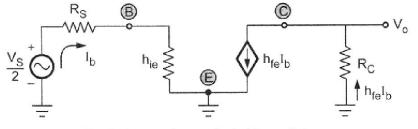

## 2. Common Mode Gain (A <sub>c</sub>)

Let the magnitude of both the a.c. input signals be VS and are in phase with each other. Hence the differential input Vd = 0 while the common mode input Vc is the average value of the two.

$$V_{c} = \frac{V_{1} + V_{2}}{2} = \frac{V_{S} + V_{S}}{2} \qquad \dots (7)$$

$$= V_{S}$$

the output can be expressed as

$$V_{o} = A_{c} V_{S} \qquad \dots (8)$$

$$A_{c} = \frac{V_{o}}{V_{S}} \qquad \dots (.8 \text{ (a)})$$

But now both the emitter currents flows through R  $_{\rm E}$  in the Same direction. Hence the total current flowing through R  $_{\rm E}$  is 2I  $_{\rm e}$ . considering only one transistor, as in the Fig

The emitter resistance is shown 2 RE in the Fig

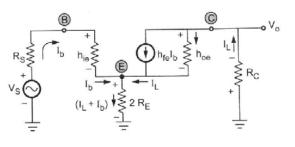

#### Fig. Approximate hybrid model

$\begin{array}{rcl} & Current \ through \ R_C &=& Load \ current \ I_L \\ & Effective \ emitter \ resistance \ &=& 2 \ R_E \\ & Current \ through \ emitter \ resistance \ &=& I_L + I_b \\ & Current \ through \ h_{oe} \ &=& (I_L - h_{fe} \ I_b) \end{array}$

Negative sign due to the assumed direction of current. Applying KVL to the output hoop,

$$\frac{-(I_L - h_{fe} I_b)}{h_{oe}} - 2 R_E (I_L + I_b) - I_L R_C = 0$$

$$-\frac{I_{L}}{h_{oe}} + \frac{h_{fe}}{h_{oe}} I_{b} - 2 R_{E} I_{L} - 2 R_{E} I_{b} - I_{L} R_{C} = 0$$

$$I_{b} \left[ \frac{h_{fe}}{h_{oe}} - 2 R_{E} \right] = I_{L} \left[ \frac{1}{h_{oe}} + 2 R_{E} + R_{C} \right]$$

$$I_{b} \left[ h_{fe} - 2 R_{E} h_{oe} \right] = I_{L} \left[ 1 + h_{oe} \left( 2 R_{E} + R_{C} \right) \right]$$

$$\cdots \qquad \frac{I_{L}}{I_{b}} = \frac{\left[ h_{fe} - 2 R_{E} h_{oe} \right]}{\left[ 1 + h_{oe} \left( 2 R_{E} + R_{C} \right) \right]} \qquad \dots (10)$$

Substituting value of I b, into the equation (8(b)), we get

$$V_{\rm S} = \frac{I_{\rm L} [1 + h_{oe} \ (2R_{\rm E} + R_{\rm C})] (R_{\rm S} + h_{ie} + 2R_{\rm E})}{[h_{fe} - 2R_{\rm E} h_{oe}]} + I_{\rm L} (2R_{\rm E})$$

$$\therefore \qquad \frac{V_{\rm S}}{I_{\rm L}} = \frac{[1 + h_{oe} \ (2R_{\rm E} + R_{\rm C})] (R_{\rm S} + h_{ie} + 2R_{\rm E})}{[h_{fe} - 2R_{\rm E} h_{oe}]} + (2R_{\rm E})$$

Finding L.C.M. and adjusting the terms, we get

$$\therefore \frac{V_{S}}{I_{L}} = \frac{2 R_{E} (1 + h_{fe}) + R_{S} (1 + 2 R_{E} h_{oe}) + h_{ie} (1 + 2 R_{E} h_{oe}) + h_{oe} R_{C} [2 R_{E} + R_{S} + h_{ie}]}{[h_{fe} - 2 R_{E} h_{oe}]}$$

$$\therefore \frac{V_{S}}{I_{L}} = \frac{2 R_{E} (1 + h_{fe}) + (R_{S} + h_{ie}) (1 + 2 R_{E} h_{oe}) + h_{oe} R_{C} [2 R_{E} + R_{S} + h_{ie}]}{[h_{fe} - 2 R_{E} h_{oe}]}$$

... (11)

Neglecting the terms of  $h_{\,oe}\;R_{\,C}$  as practically  $h_{\,oe}\;R_{\,C}$  < < 1.

$$\frac{V_{\rm S}}{I_{\rm L}} = \frac{2\,R_{\rm E}\,(1+h_{\rm fe}) + (R_{\rm S}+h_{\rm ie})\,(1+2R_{\rm E}\,h_{\rm oe})}{[h_{\rm fe} - 2R_{\rm E}\,h_{\rm oe}]} \qquad \dots (12)$$

Substituting the value of  $I_L$ , in the equation (9)

*.*...

.'.

$$V_{o} = \frac{-V_{S}(h_{fe} - 2R_{E} h_{oe}) R_{C}}{2R_{E}(1 + h_{fe}) + (R_{S} + h_{ie})(1 + 2R_{E} h_{oe})}$$

Hence the common mode gain can be written as (absorbing negative sign),

$$A_{c} = \frac{V_{o}}{V_{S}} = \frac{(2 R_{E} h_{oe} - h_{fe}) R_{C}}{2R_{E}(1 + h_{fe}) + (R_{S} + h_{ie})(1 + 2R_{E} h_{oe})} \dots (13)$$

In practice  $h_{\,oe}$  is generally neglected hence the expression for  $A_{\,c}$  can be further modified as

$$A_{e} = \frac{-h_{fe} R_{C}}{R_{S} + h_{ie} + 2 R_{E} (1 + h_{fe})} \dots (14)$$

#### **Common Mode rejection Ratio (CMRR)**

Once the differential and common mode gains are obtained, the expression for the CMRR can be obtained as,

$$CMRR = \left| \frac{A_{d}}{A_{c}} \right|$$

$$\therefore CMRR = \frac{R_{S} + h_{ie} + 2R_{E}(1 + h_{fe})}{(R_{S} + h_{ie})} \qquad \dots (15)$$

This is CMRR for dual input balanced output differential amplifier circuit.

#### **Techniques of Improving Input Impedance**

Among three configurations (CB, CC and CE), common collector or emitter follower circuit has high input impedance. Typically it is 200 K $\Omega$  to 300 K $\Omega$ . A single stage emitter follower circuit can give input impedance upto 500 K $\Omega$ . However, the input impedance considering biasing resistors is

Figure shows the direct coupling of two stages of emitter follower significantly less. Because  $Ri' = R_1 \parallel R_2 \parallel R_1$  The input impedance of the circuit can be improved by direct coupling of two stages of emitter follower amplifier. The input impedance can be increased using two techniques :

- Using direct coupling (Darlington connection)

- Using Bootstrap technique

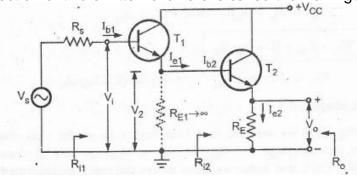

#### **Darlington Transistors**

Figure shows the direct coupling of two stages of emitter follower amplifier. This cascaded connection of two emitter followers is called the Darlington connection.

Assume that the load resistance  $R_L$  is such that  $R_L$  hoe < 0.1, therefore we can use approximate analysis method for analyzing second stage.

Figure shows approximate h-parameter (AC) equivalent circuit for common emitter configuration. The same circuit can be redrawn by making collector common to have approximate h-parameter equivalent circuit for common collector configuration.

#### Analysis of second stage :

a) Current Gain (A<sub>12</sub>):

$$A_{i2} = \frac{I_o}{I_b} = -\frac{I_e}{I_b} = \frac{I_b + h_{fe} I_b}{I_b} = \frac{I_b(1+h_{fe})}{I_b}$$

$\therefore$   $A_{i2} = 1 + h_{fe}$

b) Input Resistance (R<sub>12</sub>):  $R_{i2} = \frac{V_2}{I_{b2}}$

Applying KVL to outer loop we get,

$V_2 - I_{b2} h_{ie} - I_o R_E = 0$

$\therefore$   $V_2 = I_{b2}h_{ie} + I_o R_E$

$\therefore$   $\frac{V_2}{I_{b2}} = h_{ie} + \frac{I_o}{I_{b2}} R_E$

$\therefore$   $R_{i2} = h_{ie} + A_{i2}R_E \text{ since, } \frac{I_o}{I_{b2}} = A_{i2}$

$\therefore$   $R_{i2} = h_{ie} + (1 + h_{fe}) R_E$

$R_{i2} = (1 + h_{fe}) R_E$   $\therefore$   $h_{ie} << (1 + h_{fe}) R_E$

51

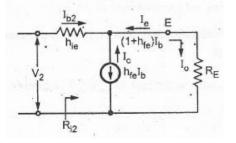

#### Analysis of first stage :

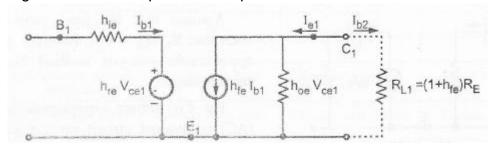

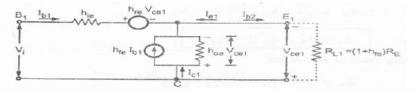

Load resistance of the first stage is the input resistance of the second stage i.e.  $R_{i2}$ . As  $R_{i2}$  is high, usually it does not meet the requirement hoe  $R_{i2} < 0.1$ , and hence we have to use the exact analysis method for analysis of the first stage. Figure shows the h-parameter equivalent circuit for common emitter configuration.

The same circuit can be redrawn by making collector common to have h-parameter collector equivalent circuit for for configuration common

a) Current Gain (A it) :

$$A_{i1} = \frac{I_{b2}}{I_{b1}}$$

$$A_{i1} = \frac{I_{e1}}{I_{b1}}$$

Τ. .

$I_{e1} = -(I_{b1} + I_{c1})$

and  $I_{c1} = h_{fe}I_{b1} + h_{oe} V_{ce1} = h_{fe}I_{b1} + h_{oe} (-I_{b2} R_{L1}) = h_{fe}I_{b1} + h_{oe} I_{e1} R_{L1}$ Substituting value of Ic1 equation we get,

$$\therefore \qquad I_{e1} = -(I_{b1} + h_{fe}I_{b1} + h_{oe} I_{e2} R_{L1}) = -I_{b1} - h_{fe}I_{b1} - h_{oe} I_{e1}R_{L1}$$

$$\therefore \quad I_{e1} + h_{oe} R_{L1} I_{e1} = -I_{b1} (1 + h_{ce})$$

$$-\frac{I_{e1}}{I_{b1}} = \frac{1 + h_{fe}}{1 + h_{oe} R_{L1}}$$

We know that,  $R_{L1} = (1 + h_{fe}) R_E$

$$A_{i1} = -\frac{I_{e1}}{I_{b1}} = \frac{1 + h_{fe}}{1 + h_{oe} (1 + h_{fo}) R_E}$$

$$= \frac{1 + h_{fe}}{1 + h_{oe} h_{fe} R_E} \because h_{fe} > > 1$$

$$I = \frac{V_i}{I_b}$$

Applying KVL to output loop we get,

$$\mathbf{V_i} - \mathbf{I_{b1}} \mathbf{h_{ie}} - \mathbf{h_{re}} \mathbf{V_{ce1}} + \mathbf{V_{ce1}} = \mathbf{0}$$

$\therefore V_i = I_{b1}h_{ic} + h_{re}V_{ce1} -$

The terms  $h_{re} V_{cel}$  is negligible since  $h_{re}$  is in the order of  $2.5 \times 10^{-4}$

$$= I_{b1}h_{ie} - (-I_{b2}R_{L1}) = I_{b1}h_{ie} + I_{b2}R_{L1}$$

$$\therefore R_{i1} = \frac{V_i}{I_{b1}} = h_{ie} + \frac{I_{b2}}{I_{b1}}R_{L1} = h_{ie} + A_{i1}R_{L1}$$

$$\therefore R_{i1} = h_{ie} + A_{i1} (1 + h_{fe}) R_E$$

and Communication Engineering Department 52

Electronics and Communication Engineering Department

Substituting value of  $A_{i1}$  we get,  $R_{i1} = \frac{V_i}{I_{b1}} = h_{ie} + \frac{(1+h_{fe})(1+h_{fe})R_E}{1+h_{oe}h_{fe}R_E}$   $\therefore \qquad R_{i1} = h_{ie} + \frac{(1+h_{fe})^2 R_E}{1+h_{oe}h_{fe}R_E}$   $\therefore \qquad R_{i1} = \frac{(1+h_{fe})^2 R_E}{1+h_{oe}h_{fe}R_E} \qquad \because h_{ie} \qquad << \qquad \frac{(1+h_{fe})^2 R_E}{1+h_{oe}h_{fe}R_E}$

#### **Overall current gain(Ai)**

$$A_i = A_{i1} \times A_{i2}$$

$$= \frac{1 + h_{fe}}{1 + h_{oe} (1 + h_{fe}) R_E} \times (1 + h_{fe})$$

$$\therefore \qquad A_i = \frac{(1 + h_{fe})^2}{1 + h_{oe} (1 + h_{fe}) R_E}$$

From table, we can say that Darlington connection improves input impedance as well as current gain of the circuit

#### **Overall Voltage gain**

| Parameter        | Single stage                                 | Darlington                                                                                    |

|------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------|

| Input resistance | $R_{i} = (1 + h_{fe}) R_{E} = 168.3 k\Omega$ | $R_{j} = \frac{(1 + h_{fe})^{2} R_{E}}{1 + h_{ce} (1 + h_{fe}) R_{E}} = 1.65 \text{ M}\Omega$ |

| Current gain     | A <sub>i</sub> = 1 + h <sub>fe</sub> = 51    | $A_{i} = \frac{(1 + h_{fe})^{2}}{1 + h_{oe} (1 + h_{fe}) R_{E}} \approx 500$                  |

We know that

$$A_{v} = \frac{A_{i}R_{L}}{R_{i}}$$

By subtracting 1 on both sides we get

$$1 - A_{v} = 1 - \frac{A_{i}R_{L}}{R_{i}}$$

$$\therefore \qquad 1 - A_{v} = \frac{R_{i} - A_{i}R_{L}}{R_{i}} = \frac{h_{ic} + h_{rc}A_{i}R_{i} - A_{i}R_{L}}{R_{i}}$$

$$= \frac{h_{ie}}{R_{i}} \text{ since } h_{ic} = h_{ie} \text{ and } h_{rc} = 1 - h_{re} \approx 1$$

$$\therefore \qquad A_{v} = 1 - \frac{h_{ie}}{R_{i}}$$

We know that the overall voltage gain in multistage amplifier is a product of individual voltage gain

$$\therefore \qquad A_{v} = A_{v1} A_{v2} = \left(1 - \frac{h_{ie}}{R_{i1}}\right) \left(1 - \frac{h_{ie}}{R_{i2}}\right)$$

$$\therefore \qquad A_{v} = 1 - \frac{h_{ie}}{R_{i2}} - \frac{h_{ie}}{R_{i1}} + \frac{h_{ie}^{2}}{R_{i1}R_{i2}}$$

As we know, input resistance Ri1 >> Ri2 we can neglect term 3 and term 4 in the above equation.

$$\dot{} \qquad \qquad A_{\rm v} \approx 1 - \frac{{\rm h}_{\rm ie}}{{\rm R}_{\rm i2}}$$

Output Impedance (Ro<sub>2</sub>) :

$$R_o = \frac{1}{Output admittance} = \frac{1}{Y_o}$$

From equation, Yo of the transistor is given as

$$Y_o = Y_{o1} = h_{oc} - \frac{h_{fc} \cdot h_{rc}}{h_{ic} + R_s} = h_{oe} - \frac{-(1 + h_{fe})}{h_{ie} + R_s}$$

S.K.P. Engineering College, Tiruvannamalai Since

$$h_{oc} = h_{oe}$$

,

$h_{fc} = -(1 + h_{fe})$

And

$$\begin{array}{rcl} h_{ic} &=& h_{ie} \\ Y_{o1} &=& h_{oe} + \frac{(1+h_{fe})}{h_{ie}+R_s} \\ Y_{o1} &=& \frac{1+h_{fe}}{h_{ic}+R_s} \\ \ddots & & h_{oe} &<< \frac{(1+h_{fe})}{h_{ic}+R_s} \\ \therefore & & R_{o1} &=& \frac{1}{Y_{o1}} \\ \ddots & & & R_{o1} = \frac{h_{ie1}+R_s}{1+h_{fe}} \end{array}$$

we can see that the  $R_{i1}$  of the first stage is the source

Resistance for second stage, i.e.  $R_{S2} = \left(\frac{R_{O1}}{h_{ie1} + R_s}\right)_{+ h_{ie1}}$

Since the current in  $T_2$  is  $1+h_{fe}$  times the current in  $T_1$ ,  $h_{ie1} \approx (1+h_{fe})h_{ie2}$  substituting this value of  $h_{ie1}$  in equation 15 we get,

$$R_{o2} = \frac{(1+h_{fe})h_{ie2} + R_s}{(1+h_{fe})^2} + \frac{h_{ie2}}{1+h_{fe}} = \frac{h_{ie2}}{1+h_{fe}} + \frac{R_s}{(1+h_{fe})^2} + \frac{h_{ie2}}{1+h_{fe}}$$

$$R_{o2} = \frac{R_s}{(1+h_{fe})^2} + \frac{2h_{ie2}}{(1+h_{fe})}$$

#### Key Point:

*.*.

- In above analysis we have assumed that the h-parameter of T1 and T2 are identical,

- From the above analysis we have seen that Darlington connection of two transistors improves current gain and input resistance of the circuit.

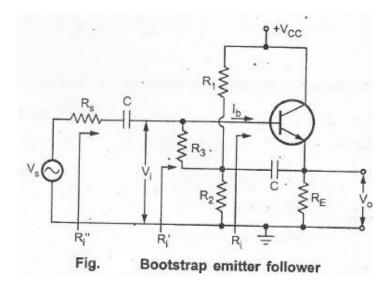

#### 16. Explain about Bootstrap Emitter Follower technique.[CO2-H2]

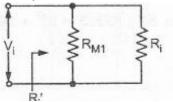

In emitter follower, the input resistance of the amplifier is reduced because of the shunting effect of the biasing resistors. To overcome this problem the emitter follower circuit is modified, as shown in the Figure. Here, two additional components are used, resistance R, and capacitor C .The capacitor, is connected between the emitter and the junction of R1,R2 and R3.

For d.c. signal, capacitor C acts as a open circuit and therefore resistance R1,R2 and R3 provides necessary biasing to keep the transistor in active region.

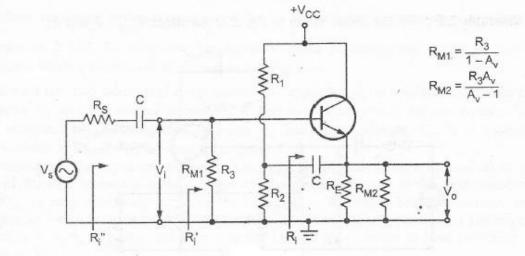

For ac signal, the capacitor acts as a short circuit. Its value is chosen such that it provides very low reactance nearly short circuit at lowest operating frequency. Hence for ac, the bottom of R3 is effectively connected to the output(the emitter), whereas the top of R3 is at the -input. (the base). In other words, R3 is connected between input node and output node. For such connection effective input resistance is given by Miller's theorem.

The two components are

and

R3 is the impedance between output voltage and input voltage and K is the voltage gain.

These are

$$R_{M1} = \frac{R_3}{1 - A_v}$$

and  $R_{M2} = \frac{R_3 A_v}{A_v - 1}$

Since, for an emitter follower, Av, approaches unity, then R<sub>M2</sub> becomes extremely large.

$$R'_i = R_i \parallel R_M$$

$R_{i} = h_{ie} + (1 + h_{fe}) R_{E}$