# **SKP Engineering College**

Tiruvannamalai – 606611

A Course Material

on

**Electronic Devices**

By

K.Vijayalakshmi

**Assistant Professor**

**Electronics and Communication Engineering Department**

#### **Quality Certificate**

This is to Certify that the Electronic Study Material

Subject Code: EC6201

Subject Name: Electronic Devices

Year/Sem: I/II

Being prepared by me and it meets the knowledge requirement of the University curriculum.

Signature of the Author Name: K.Vijayalakshmi Designation: Assistant Professor

This is to certify that the course material being prepared by Ms. K.Vijayalakshmi is of the adequate quality. He has referred more than five books and one among them is from abroad author.

| Signature of HD | Signature of the Principal     |

|-----------------|--------------------------------|

| Name:           | Name: Dr.V.Subramania Bharathi |

| Seal:           | Seal:                          |

9

9

9

#### EC6201 ELECTRONIC DEVICES

#### LTPC 3 0 0 3

#### **OBJECTIVES:** The student should be made to:

Be exposed to basic electronic devices

Be familiar with the theory, construction, and operation of Basic electronic devices.

#### UNIT I SEMICONDUCTOR DIODE

PN junction diode, Current equations, Diffusion and drift current densities, forward and reverse bias characteristics, Switching Characteristics.

#### UNIT II BIPOLAR JUNCTION

NPN -PNP -Junctions-Early effect-Current equations – Input and Output characteristics of CE, CB CC-Hybrid - $\pi$  model - h-parameter model, Ebers Moll Model-Gummel Poon-model, Multi Emitter Transistor.

#### UNIT III FIELD EFFECT TRANSISTORS

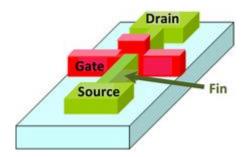

JFETs – Drain and Transfer characteristics,-Current equations-Pinch off voltage and its significance- MOSFET- Characteristics- Threshold voltage -Channel length modulation, D-MOSFET, E-MOSFET-, Current equation - Equivalent circuit model and its parameters, FINFET,DUAL GATE MOSFET.

#### UNIT IV SPECIAL SEMICONDUCTOR DEVICES 9

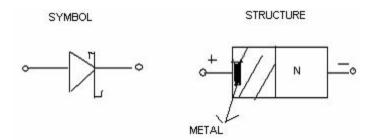

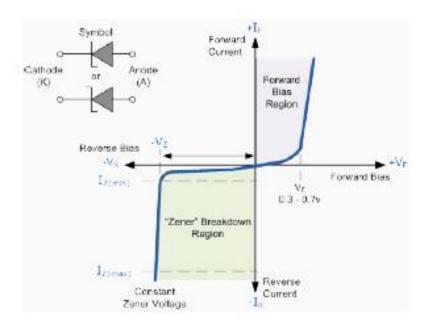

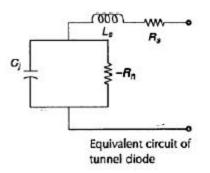

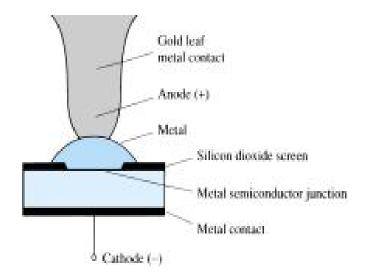

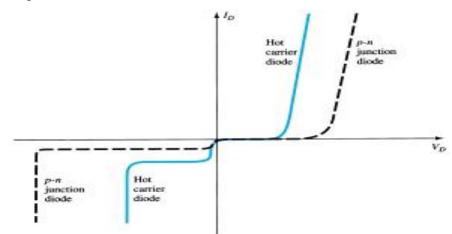

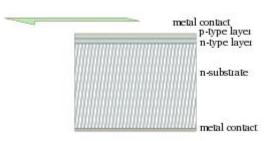

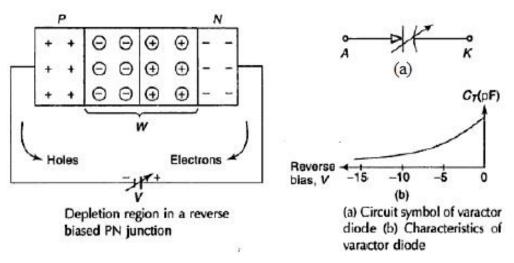

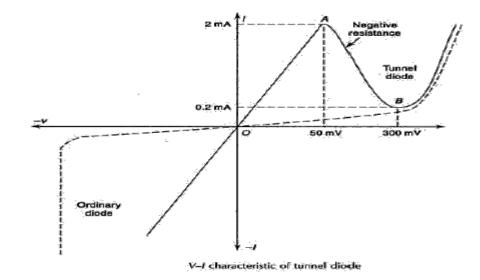

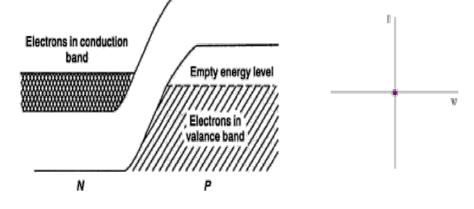

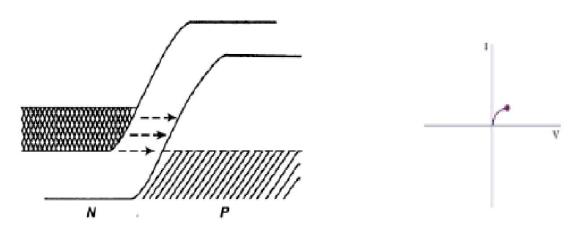

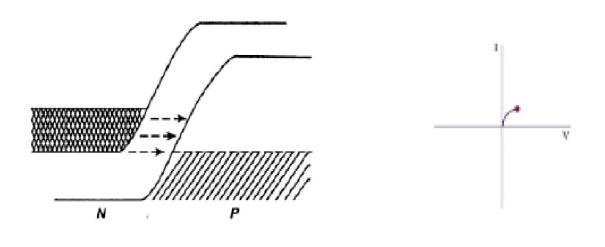

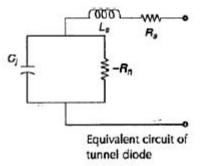

Metal-Semiconductor Junction- MESFET, Schottky barrier diode-Zener diode-Varactor diode – Tunnel diode- Gallium Arsenide device, LASER diode, LDR.

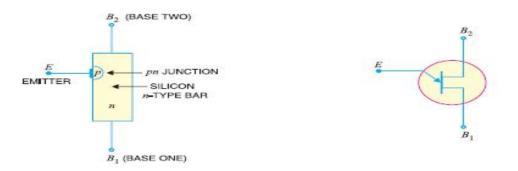

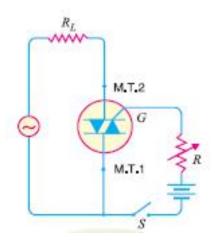

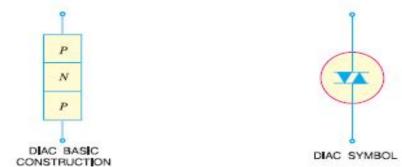

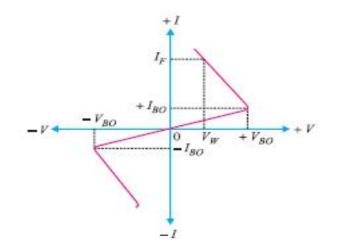

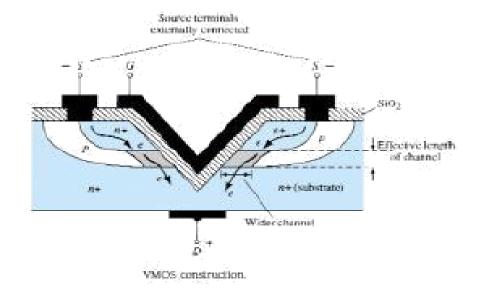

#### UNIT V POWER DEVICES AND DISPLAY DEVICES

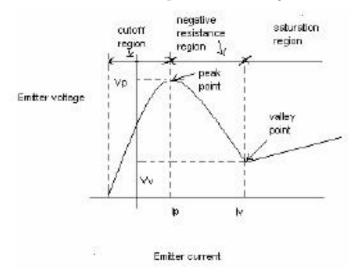

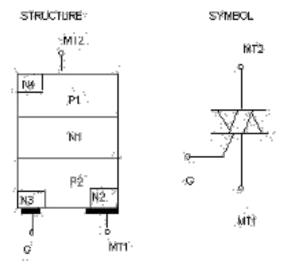

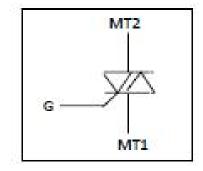

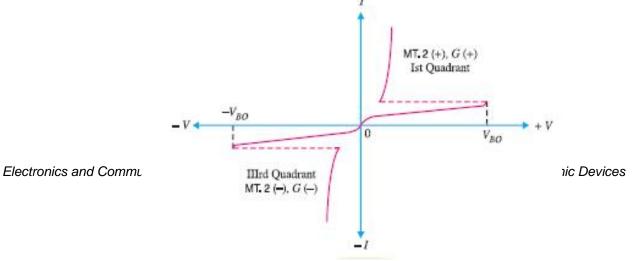

UJT, SCR, Diac, Triac, Power BJT- Power MOSFET- DMOS-VMOS. LED, LCD, Photo transistor, Opto Coupler, Solar cell, CCD.

#### **TOTAL PERIODS: 45**

#### OUTCOMES: At the end of the course, the student should be able to:

Explain the theory, construction, and operation of basic electronic devices.

$\Box$  Use the basic electronic devices

#### TEXT BOOKS

1. Donald A Neaman, "Semiconductor Physics and Devices", Third Edition, Tata Mc GrawHill Inc. 2007.

#### **REFERENCES:**

1. Yang, "Fundamentals of Semiconductor devices", McGraw Hill International Edition, 1978.

2. Robert Boylestad and Louis Nashelsky, "Electron Devices and Circuit Theory" Pearson Prentice Hall, 10th edition, July 2008.

# CONTENTS

| S.No | Particulars | Page |  |

|------|-------------|------|--|

| 1    | Unit – I    | 5    |  |

| 2    | Unit – II   | 28   |  |

| 3    | Unit – III  | 54   |  |

| 4    | Unit – IV   | 78   |  |

| 5    | Unit – V    | 102  |  |

#### Unit - I

# Semiconductor Diode

#### Part - A

#### 1. What are semiconductors?

The materials whose electrical property lies between those of conductors and insulators are known as Semiconductors. Ex germanium, silicon.

It has two types.

1. Intrinsic semiconductor 2. Extrinsic semiconductor.

# 2. Differentiate between intrinsic and extrinsic semiconductor [CO1–L2 -

#### May/June 2014]

Pure form of semiconductors are said to be intrinsic semiconductor.

Ex: germanium, silicon.

It has poor conductivity

If certain amount of impurity atom is added to intrinsic semiconductor the resulting semiconductor is Extrinsic or impure Semiconductor

It has good conductivity.

### 3. Define drift current? [CO1 – L1 - May/June 2012]

When an electric field is applied across the semiconductor, the holes move towards the negative terminal of the battery and electron move towards the positive terminal of the battery. This drift movement of charge carriers will result in a current termed as drift current.

#### 4. Give the expression for drift current density [CO1-L2 - Nov/Dec 2013]

Drift current density due to electrons

$$Jn = q n \mu nE$$

Where,

Jn - drift current density due to electron q- Charge of electron

µn - Mobility of electron E - applied electric field

Drift current density due to holes.

Where,

Jn - drift current density due to holes q - Charge of holes

µp - Mobility of holes E - applied electric field

#### 5. Define the term diffusion current? [CO1 – L1 - May/June 2011]

A concentration gradient exists, if the number of either electrons or holes is greater in one region of a semiconductor as compared to the rest of the region. The holes and electron tend to move from region of higher concentration to the region of lower concentration. This process in called diffusion and the current produced due this movement is diffusion current.

#### 6. Give the expression for diffusion current density[CO1 – L2 - May/June 2014]

Diffusion current density due to electrons

$$Jn = q Dn dn / dx$$

Electronics and Communication Engineering Department

#### Where

Jn - diffusion current density due to electron q - Charge of an electron Dn – diffusion constant for electron dn / dx – concentration gradient Diffusion current density due to holes

$$Jp = -q Dp dp / dx$$

Where

Jp - diffusion current density due to holes q - Charge of a hole

Dp – diffusion constant for hole dn / dx – concentration gradient

# 7. Differentiate between drift and diffusion currents. [CO1 – L2 - Nov/Dec 2014] Drift current

1. It is developed due to potential gradient.

2. This phenomenon is found both in metals and semiconductors

**Diffusion current**

- 1. It is developed due to charge concentration gradient.

- 2. This phenomenon is found only in metals

# 8. What is depletion region in PN junction? [CO1 – L1 - May/June 2013]

The region around the junction from which the mobile charge carriers (electrons and holes) are depleted is called as depletion region. since this region has immobile ions, which are electrically charged, the depletion region is also known as space charge region.

### 9. What is barrier potential? [CO1 –L1]

Because of the oppositely charged ions present on both sides of PN junction an electric potential is established across the junction even without any external voltage source which is termed as barrier potential.

### 10. What is Reverse saturation current? [CO1 – L1 - May/June 2011]

The current due to the minority carriers in reverse bias is said to be reverse saturation current. This current is independent of the value of the reverse bias voltage.

# 11. What is the total current at the junction of pn junction diode? [CO1 - L2 - May/June 2015]

The total in the junction is due to the hole current entering the n material and theelectron current entering the p material. Total current is given by

$$I = Ipn(0) + Inp(0)$$

Where,

I – Total current

Ipn(0) - hole current entering the n material

Inp(0) - electron current entering the p material

### 12. Give the diode current equation? [CO1 – L1 - May/June 2015]

The diode current equation relating the voltage V and current I is given by

$$I = I_0 \left[ e^{(v)} \eta v T \right] - 1$$

where

I - diode current

$\mathsf{I}_{\mathsf{O}}-\mathsf{diode}$  reverse saturation current at room temperature

- V-External voltage applied to the dioden a constant, 1 for Ge and 2 for Si

- $V_T = kT/q = T/11600$ , thermal voltage

- K Boltzmann's constant (1.38066x10^-23 J/K)

- q Charge of electron (1.6x10^-19 C)

- T Temperature of the diode junction

#### 13. What is recovery time? Give its types. [CO1 – L2 - Nov/Dec 2013]

When a diode has its state changed from one type of bias to other a transient accompanies the diode response, i.e., the diode reaches steady state only after an interval of time " tr" called as recovery time. The recovery time can be divided in to two types such as

- (i) forward recovery time

- (ii) reverse recovery time

#### 14. Define storage time. [CO1 – L1]

The interval time for the stored minority charge to become zero is called storage time. It is represented as  $t_s$ .

#### 15. Define transition time. [CO1 – L1]

The time when the diode has normally recovered and the diode reverse current reaches reverse saturation current lo is called as transition time. It is represented as  $t_t$

#### 16. Define PIV. [CO1 – L1]

Peak inverse voltage is the maximum reverse voltage that can be applied to the PN junction without damage to the junction.

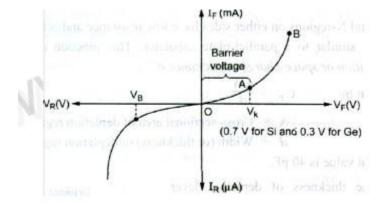

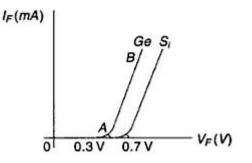

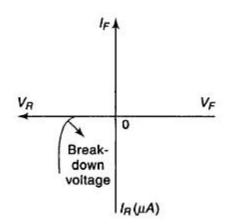

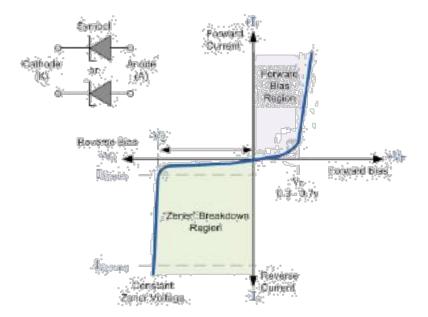

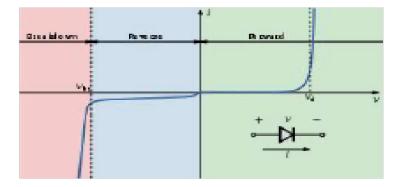

### 17. Draw V-I characteristics of pn diode[CO1 – L2 - May/June 2014]

**18. Write the application of PN diode [CO1 – L3 - Nov/Dec 2014]** Can be used as rectifier in DC Power Supplies.

- In Demodulation or Detector Circuits.

- In clamping networks used as DC Restorers

- In clipping circuits used for waveform generation.

- As switches in digital logic circuits.

- In demodulation circuits.

#### PART B

# 1. Explain the drift and diffusion currents for PN diode. [CO1 – L2 - May/June 2014] [8]

#### **Drift and Diffusion Currents:**

The flow of charge (ie) current through a semiconductor material are of two types namely drift & diffusion.

(ie) The net current that flows through a (PN junction diode) semiconductor material has two components

Drift current

#### **Drift Current:**

$\rightarrow$  When an electric field is applied across the semiconductor material, the charge carriers attain a certain drift velocity V<sub>d</sub>, which is equal to the product of the mobility of the charge carriers and the applied Electric Field intensity E;

Drift velocity  $V_d$  = mobility of the charge carriers X Applied Electric field intensity

$\rightarrow$  Holes move towards the negative terminal of the battery and electrons move towards the positive terminal of the battery. This combined effect of movement of the charge carriers constitutes a current known as — the drift current — .

$\rightarrow$  Thus the drift current is defined as the flow of electric current due to the motion of the charge carriers under the influence of an external electric field.

$\rightarrow$  Drift current due to the charge carriers such as free electrons and holes are the current passing through a square centimeter perpendicular to the direction of flow.

(i) Drift current density J<sub>n</sub>, due to free electrons is given

by

$$J_n = q n \mu_n E A / cm^2$$

#### (ii) Drift current density J<sub>P</sub>, 2due to holes is given by

$J_P = q p \mu_p E A / cm$

Where, n - Number of free electrons per cubic centimeter.

P - Number of holes per cubic centimeter

$\mu$  n – Mobility of electrons in cm<sup>2</sup> / Vs

$$\mu$$

p – Mobility of holes in cm<sup>2</sup> / Vs

E – Applied Electric filed Intensity in V /cm

$q - Charge of an electron = 1.6 \times 10^{-19} coulomb.$

#### **Diffusion Current:**

$\rightarrow$  It is possible for an electric current to flow in a semiconductor even in the absence of the applied voltage provided a concentration gradient exists in the material.

$\rightarrow$  A concentration gradient exists if the number of either elements or holes is greater in one region of a semiconductor as compared to the rest of the Region.

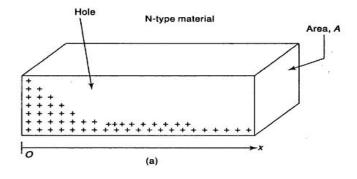

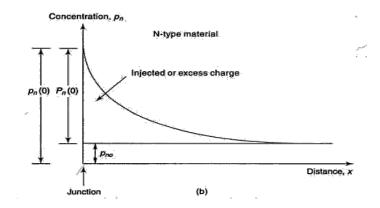

(a) Exess hole concentration varying along the axis in an N-type semiconductor bar

#### (b) The resulting diffusion current

$\rightarrow$  In a semiconductor material the change carriers have the tendency to move from the

region of higher concentration to that of lower concentration of the same type of charge carriers. Thus the movement of charge carriers takes place resulting in a current called diffusion current.

As indicated in fig a, the hole concentration p(x) in semiconductor bar varies from a high value to a low value along the x-axis and is constant in the y and z directions.

Diffusion current density due to holes Jp is given by

$$J_p = -qD_p \frac{dp}{dx} A/cm^2$$

Since the hole density p(x) decreases with increasing x as shown in fig b, dp/dx is negative and the minus sign in equation is needed in order that  $J_p$  has positive sign in the positive x direction.

Diffusion current density due to the free electrons is given by

Where dn/dx - concentration gradient for electrons

Dp/dx - concentration gradient for holes

$$J_n = q D_n \frac{dn}{dx} A / cm^2$$

$D_n$  and  $D_p$  – diffusion coefficient for electrons and holes

# **Total Current:**

The total current in a semiconductor is the sum of both drift and diffusion currents that is given by

$$J_p = qP\mu_p E - qD_p \frac{dp}{dx}$$

Similarly the total current density for an N type semiconductor is given by

$$J_n = qn\mu_n E - qD_n \frac{dn}{dx}$$

# 2. Derive the PN diode current equation.[CO1 – L2 - May/June 2015] [6]

#### **Diode Current Equation:**

The diode current equation relating the voltage V and current I is given by where

I - diode current

$I_{\rm o}$  – diode reverse saturation current at room temperature V – external voltage applied to the diode

$\Pi$  - a constant, 1 for Ge and 2 for Si V<sub>T</sub> = kT/q = T/11600, thermal voltage

K – Boltzmann's constant (1.38066x10^-23 J/K) q – charge of electron (1.6x10^-19 C)

T – temperature of the diode junction

At room temperature (T=300 K),  $V_T = 26$ mV. Substituting this value in current equation,

$$I = I_0 \left[ e^{\frac{40v}{\eta}} - 1 \right]$$

For germanium diode,

$$I = I_0 [e^{40v} - 1]$$

since  $\eta = 1$  for Ge

For silicon diode,

$I=I_0\left[e^{20v}-1

ight]$  since  $\eta=$ 1 for si

If the value of applied voltage is greater than unity, then the equation of diode current for germanium,  $I_0[e^{40\nu}]$

and for silicon,

$I_0[e^{20\nu}]$

when the diode is reverse biased, its current equation may be obtained by changing the sign of voltage V. Thus diode current with reverse bias is  $I = I_0 \left[ e^{(-\nu)} \eta v T \right] - 1$

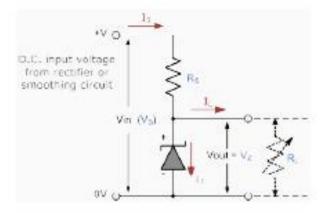

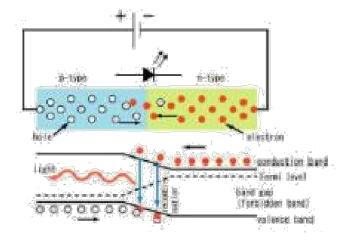

3. Explain the operation of PN junction under forward bias condition with itscharacteristics. [CO1 – L2 - May/June 2014][8]

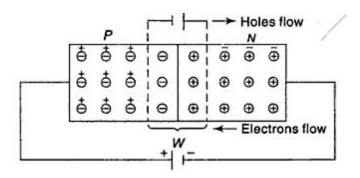

#### Forward Bias Condition:

When positive terminal of the battery is connected to the P-type and negative terminal to N-type of the PN junction diode that is known as forward bias condition.

### Operation

The applied potential in external battery acts in opposition to the internal potential barrier which disturbs the equilibrium.

As soon as equilibrium is disturbed by the application of an external voltage, the Fermi level is no longer continuous across the junction.

Under the forward bias condition the applied positive potential repels the holes in P type region so that the holes move towards the junction and the applied positive potential repels the electrons in N type region so that the electrons move towards the junction.

When the applied potential is more than the internal barrier potential the depletion region and internal potential barrier disappear.

#### **V-I Characteristics**

Electronics and Communication Engineering Department

As the forward voltage increased for  $V_F < V_0$ , the forward current  $I_F$  almost zero because the potential barrier prevents the holes from P region and electrons from N region to flow across the depletion region in opposite direction.

For  $V_F > V_0$ , the potential barrier at the junction completely disappears and hence, the holes cross the junction from P to N type and electrons cross the junction to opposite direction, resulting

large current flow in external circuit.

A feature noted here is the cut in voltage or threshold voltage  $V_F$  below which the current is very small.

At this voltage the potential barrier is overcome and the current through the junction starts to increase rapidly.

Cut in voltage is 0.3V for germanium and 0.7 for silicon.

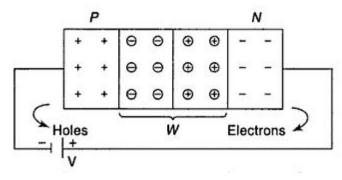

# 4. Explain the operation of PN junction under reverse bias condition with its Characteristics. [CO1 – L2 - May/June 2012] (8) Under Reverse Bias Condition:

When the negative terminal of the battery is connected to the P-type and positive terminal to N-type of the PN junction diode that is known as forward bias condition.

#### Operation

The holes from the majority carriers of the P side move towards the negative terminal of the battery and electrons which from the majority carrier of the N side are attracted towards the positive terminal of the battery.

Hence, the width of the depletion region which is depleted of mobile charge carriers increases. Thus, the electric field produced by applied reverse bias, is in the same direction as the electric field of the potential barrier.

Hence the resultant potential barrier is increased which prevents the flow of majority carriers in both directions. The depletion width W is proportional to under reverse bias.

#### **V-I characteristics**

Theoretically no current flow in the external circuit. But in practice a very small amount of current of the order of few microamperes flows under reverse bias.

Electrons forming covalent bonds of semiconductor atoms in the P and N type regions may absorb sufficient energy from heat and light to cause breaking covalent bonds. So electron hole pairs continuously produced.

Consequently the minority carriers electrons in the P region and holes in the N region, wander over to the junction and flow towards their majority carrier side giving rise a small reverse current. This current is known as reverse saturation current lo.

The magnitude of this current is depends on the temperature because minority carrier is thermally broken covalent bonds.

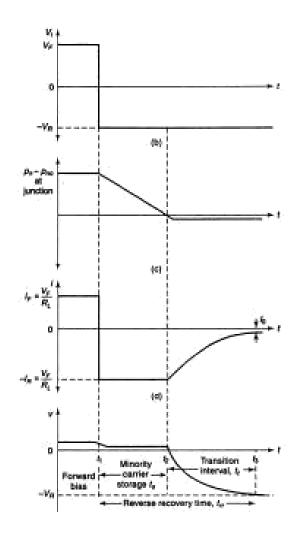

# 5. Explain details about the switching characteristics on PN diode with neat Sketch. [CO1 – L2 - May/June 2015] [12]

Diodes are often used in switching mode. When the applied bias voltage to the PN diode is suddenly reversed in opposite direction and it reaches a steady state at a interval of time that is called the recovery time.

Forward recovery time is defined is the time required the forward voltage or current to reach a specified value after switching diode from its reverse to forward biased state.

When PN diode is forward biased the minority electrons concentration in P region is linear. If the junction is suddenly reversed at t1 then because of stored electronic charge, the reverse current  $I_R$  is initially of the same magnitude as forward current  $I_F$ .

The diode will continue to conduct until the injected or excess minority carrier density (p-po) or (n-no) has dropped to zero shown in fig. c.

In fig. b the applied voltage Vi = V<sub>F</sub> for the time up to t1 is in the direction to forward bias the diode. The resistance  $R_L$  is large so that the drop across  $R_L$  is large when compared to the drop across diode. Then the current is I= V<sub>F</sub> /  $R_L$  = I<sub>F</sub>.

At time t=t1 the input voltage is reversed to the value of  $-V_R$  current does not become zero and the value is I=  $V_R / R_L = I_R$  shown in fig d.

During the time interval from t1 to t2 the injected minority carriers have remained stored and hence this interval is called the storage time (t1).

After the instant t=t2, the diode gradually recovers and ultimately reaches the steady state. The time interval between t2 and instant t3 when the diode has recovered nominally is called the transition time  $t_t$ .

The recovery said to have completed (i) when even the minority carriers remote from the junction have difference to the junction and crossed it. (ii) when the junction transition capacitance C across the reverse biased junction has got charged through the external resistor  $R_L$  to the voltage  $-V_R$ .

For commercial switching type diodes the reverse recovery time  $t_{rr}$  ranges from less than 1ns up to as high as 1us.

In order to minimize the effect of reverse current the time period of the operating frequency should be a minimum of approximately 10 times  $t_{rr}$ . For example if diode has  $t_{rr}$  of 2ns its operating frequency is

The reverse recovery time can be reduced b shortening the length of the P region in a PN junction diode.

The stored storage and switching time can be reduced by introduction of gold impurities into junction diode by diffusion. The gold dopant also called a life time killer, increases the recombination rate and removes the stored minority carriers. This technique is used to produce diodes and other active devices for high speed applications.

# 6. Explain the theory of PN Junction Diode. [CO1 – L2 - May/June 2012] [16] PN Junction:

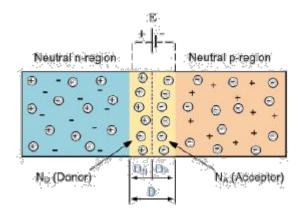

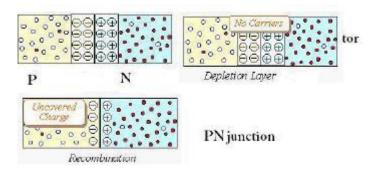

When the N and P-type semiconductor materials are first joined together a very large density gradient exists between both sides of the junction so some of the free electrons from the donor impurity atoms begin to migrate across this newly formed junction to fill up the holes in the P-type material producing negative ions. However, because the electrons have moved across the junction from the N-type silicon to the P-type silicon, they leave behind positively charged donor ions (ND) on the negative side and now the holes from the acceptor impurity migrate across the junction in the opposite direction into the region are there are large numbers of free electrons. As a result, the charge density of the P-type along the junction is filled with negatively charged acceptor ions (NA), and the charge density of the N-type along the junction is known as diffusion.

This process continues back and forth until the number of electrons which have crossed the junction have a large enough electrical charge to repel or prevent any more carriers from crossing the junction. The regions on both sides of the junction become depleted of any free carriers in comparison to the N and P type materials away from the junction. Eventually a state of equilibrium (electrically neutral situation) will occur producing a "potential barrier" zone around the area of the junction as the donor atoms repel the holes and the acceptor atoms repel the electrons. Since no free charge carriers can rest in a position where there is a potential barrier the regions on both sides

of the junction become depleted of any more free carriers in comparison to the N and P type materials away from the junction. This area around the junction is now called the Depletion Layer.

#### The Pn Junction

The total charge on each side of the junction must be equal and opposite to maintain a neutral charge condition around the junction. If the depletion layer region has a distance D, it therefore must therefore penetrate into the silicon by a distance of Dp for the positive side, and a distance of Dn for the negative side giving a relationship between the two of Dp.NA = Dn.ND in order to maintain charge neutrality also called equilibrium.

#### **PN Junction Distance:**

As the N-type material has lost electrons and the P-type has lost holes, the Ntype material has become positive with respect to the P-type. Then the presence of impurity ions on both sides of the junction cause an electric field to be established across this region with the N-side at a positive voltage relative to the P-side. The problem now is that a free charge requires some extra energy to overcome the barrier that now exists for it to be able to cross the depletion region junction. This electric field created by the diffusion process has created a "built-in potential difference" across the junction with an open-circuit (zero bias) potential of:

$E_0 = V_T \ln \left( N_D N_A / n_i^2 \right)$

Where: Eo is the zero bias junction voltage, VT the thermal voltage of 26mV at room temperature, ND and NA are the impurity concentrations and ni is the intrinsic concentration.

A suitable positive voltage (forward bias) applied between the two ends of the PN junction can supply the free electrons and holes with the extra energy. The external voltage required to overcome this potential barrier that now exists is very much dependent upon the type of semiconductor material used and its actual temperature. Typically at room temperature the voltage across the depletion layer for silicon is about 0.6 - 0.7 volts and for germanium is about 0.3 - 0.35 volts. This potential barrier will always exist even if the device is not connected to any external power source.

The significance of this built-in potential across the junction, is that it opposes both the flow of holes and electrons across the junction and is why it is called the potential barrier. In practice, a PN junction is formed within a single crystal of material rather than just simply joining or fusing together two separate pieces. Electrical contacts are also fused onto either side of the crystal to enable an electrical connection to be made to an external circuit. Then the resulting device that has been made is called a PN junction Diode or Signal Diode.

#### **Depletion Layer PN Junction:**

If one side of crystal pure semiconductor Si(silicon) or Ge(Germanium) is doped with acceptor impurity atoms and the other side is doped with donor impurity atoms, a PN junction is formed as shown in figure.P region has high concentration of holes and N region contains large number of electrons.

As soon as the junction is formed, free electrons and holes cross through the junction by the process of diffusion.During this process, the electrons crossing the junction from N- region into P-region, recombine with holes in the P-region very close to the junction.Similarly holes crossing the junction from the P-region into the N-region, recombine with electrons in the N-region very close to the junction. Thus a region is formed, which does not have any mobile charge very close to the junction. This region is called the depletion layer of pn junction.

In this region, on the left side of the junction, the acceptor atoms become negative ions and on the right side of the junction, the donor atoms become positive ions as shown in figure.

#### Function Of Depletion Layer Of PN Junction:

An electric field is set up, between the donor and acceptor ions in the depletion layer of the pn junction .The potential at the N-side is higher than the potential at P-side.Therefore electrons in the N- side are prevented to go to the lower potential of P-side. Similarly, holes in the P-side find themselves at a lower potential and are prevented to cross to the N-side. Thus, there is a barrier at the junction which opposes the movement of the majority charge carriers. The difference of potential from one side of the barrier to the other side of the barrier is called potential barrier. The potential barrier is approximately 0.7V for a silicon PN junction and 0.3V for germanium PN junction. The distance from one side of the barrier to the other side is called the width of the barrier, which depends on the nature of the material.

### <u>Unit - II</u>

### **Bipolar Junction**

# <u> Part - A</u>

# 1. Why an ordinary transistor is called bipolar? [CO2 – L2 - May/June 2012]

The operation of the transistor depends on both majority and minority carriers. So it is called bipolar device.

# 2. Collector region of transistor is larger than emitter. Why? [CO2 – L2 - May/June 2014]

Collector is made physically larger than emitter and base because collector is to dissipate much power.

# 3. Why is BJT is called current controlled device? [CO2 – L2 - Nov/Dec 2013]

The output voltage, current, or power is controlled by the input current in a transistor. So it is called the current controlled device.

# 4. Define Early Effect. [CO2 – L1 - May/June 2015]

A variation of the base-collector voltage results in a variation of the quasi-neutral width in the base. The gradient of the minority-carrier density in the base therefore changes, yielding an increased collector current as the collector-base current is increased. This effect is referred to as the Early effect.

# 5. Among CE, CB, CC which one is most popular. Why? [CO2 – L2 - May/June 2012]

CE is most popular among the three because it has high gain compared to base and collector configuration. It has the gain about to 500 that finds excellent usage in audio frequency applications.

### 7. Compare CE, CB, CC. [CO2 – L2 - May/June 2015]

| Property         | СВ                | CE                  | CC                   |  |

|------------------|-------------------|---------------------|----------------------|--|

| Input resistance | Low (about 100    | Moderate (about 750 | High (about 750 VS1) |  |

| fl)              |                   | Q)                  |                      |  |

| Output resistanc | e High (about 450 | kQ) Moderate (about | Low (about 25 O)     |  |

| 45 kfJ)          |                   |                     |                      |  |

| Current gain     | I                 | High                | High                 |  |

| Voltage gain     | About 150         | About 500           | Less than 1          |  |

| Phase shift      | 0 or 360°         | 180°                | 0 or 360°            |  |

| between input &  |                   |                     |                      |  |

| output voltages  |                   |                     |                      |  |

| Applications     | for high          | for audio frequency | for impedance        |  |

| frequency        |                   |                     |                      |  |

| circu            | uits              | circuits            | matching             |  |

| l1               | •                 |                     |                      |  |

# 8. Why h parameter model is important for BJT [CO2 – L2 - May/June 2014]

It is important because:

- 1. its values are used on specification sheets

- 2. it is one model that may be used to analyze circuit behavior

- 3. it may be used to form the basis of a more accurate transistor model

# 9. Define current amplification factor [CO2 – L1 - May/June 2012]

In a transistor amplifier with a.c. input signal, the ratio of change in output current to be the change in input current is known as the current amplification factor.

In the CB configuration the current amplification factor, $\alpha = \frac{\Delta I_c}{\Delta I_E}$ In the CE configuration the current amplification factor, $\beta = \frac{\Delta I_c}{\Delta I_B}$ In the CC configuration the current amplification factor, $\gamma = \frac{\Delta I_E}{\Delta I_B}$

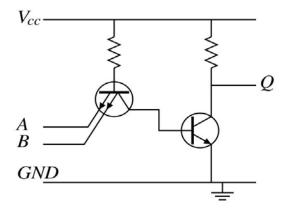

**10. What do you meant by multi emitter transistor? [CO2 – L2 - May/June 2014] Transistor–transistor logic (TTL)** is a class of digital circuits built from bipolar junction transistors (BJT) and resistors. It is called *transistor–transistor logic* because both the logic gating function (e.g., AND) and the amplifying function are performed by transistors.

TTL is notable for being a widespread integrated circuit (IC) family used in many applications such as computers, industrial controls, test equipment and instrumentation, consumer electronics, synthesizers, etc.

11. In a CR connection, the value of  $I_E$  is 6.28 mA and the collector current lc is 6.20 mA. Determine d.c. current gain. [CO2 – L3 - May/June 2013]

$I_E = 6.28$ mA and Ic = 6.20mA

We know that common base dc current gain

$$\alpha = \frac{I_C}{I_E}$$

$$= \frac{6.20 * 10^{-3}}{6.28 * 10^{-3}} = 0.987$$

12. The transistor has  $I_E = 10$  mA and  $\alpha = 0.98$ . Find the value of base and collector currents. [CO2 – L3 - Nov/Dec2012]  $I_E=10$ mA and  $\alpha=0.98$

Electronics and Communication Engineering Department 31 Electronic Devices

The common base dc current gain,

$$\alpha = \frac{I_C}{I_E}$$

$$0.98 = \frac{I_C}{10}$$

$$I_C = 0.98 * 10 = 9.8mA$$

The Emitter current I<sub>E</sub>=I<sub>B</sub>+I<sub>C</sub>

$$10 = I_B + I_C$$

$$10 = I_B + 9.8$$

$$I_B = 0.2mA$$

13. If a transistor has a  $\alpha$  of 0.97 find the value of  $\beta$ . If  $\beta$ =200, find the value of  $\alpha$ . [CO2 – L3 - May/June 2015]

lf

$$\alpha = 0.97, \beta = \frac{\alpha}{1 - \alpha} = \frac{0.97}{1 - 0.97} = 32.33$$

If  $\beta = 200, \alpha = \frac{\beta}{1 + \beta} = \frac{200}{1 + 200} = 0.995$

#### 14. Give some applications of BJT. [CO2 – L3 - May/June 2012]

The BJT remains a device that excels in some applications, such as discrete circuit design, due to the very wide selection of BJT types available, and because of its high transconductance and output resistance compared to MOSFETs.

The BJT is also the choice for demanding analog circuits, especially for very-highfrequency applications, such as radio-frequency circuits for wireless systems. Bipolar transistors can be combined with MOSFETs in an integrated circuit by using a BICMOS process of wafer fabrication to create circuits that take advantage of the application strengths of both types of transistor.

#### PART B

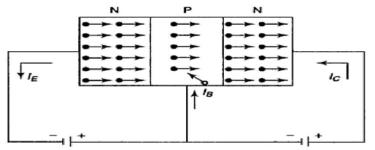

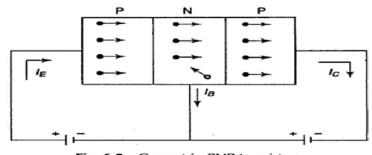

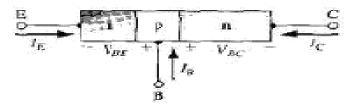

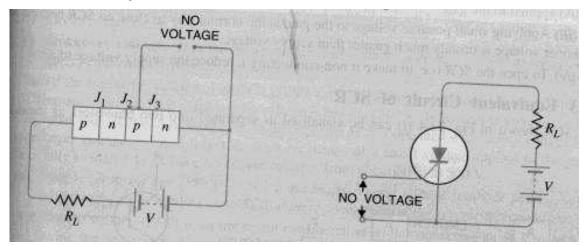

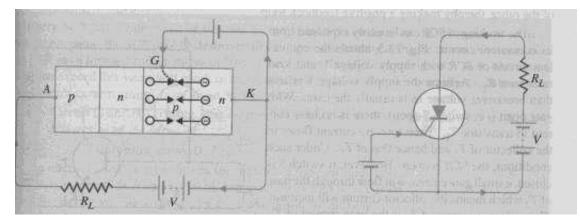

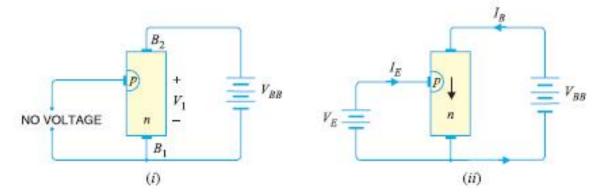

# 1. Explain the operation of NPN and PNP transistors [CO2 – L2 - May/June 2014] [8]

**Transistor Operation:** The basic operation will be described using the pnp transistor. The operation of the pnp transistor is exactly the same if the roles played by the electron and hole are interchanged.

• One p-n junction of a transistor is reverse-biased, whereas the other is forward-biased

Fig. 6.4 Current in NPN transistor

Fig. 6.5 Current in PNP transistor

• Both biasing potentials have been applied to a pnp transistor and resulting majority and Minority carrier flows indicated.

• Majority carriers (+) will diffuse across the forward-biased p-n junction into the n-type Material.

• A very small number of carriers (+) will through n-type material to the base terminal. Resulting IB is typically in order of microamperes.

• The large number of majority carriers will diffuse across the reverse-biased junction into the p-type material connected to the collector terminal.

• Majority carriers can cross the reverse-biased junction because the injected majority carriers will appear as minority carriers in the n-type material.

• Applying KCL to the transistor :

$$I_E = I_C + I_B$$

• The comprises of two components – the majority and minority carriers

$I_{C} = I$  majority +  $I_{CO}$  minority

•  $I_{CO} - I_C$  current with emitter terminal open and is called leakage current.

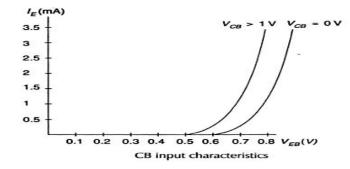

2. Explain the input and output characteristics of a transistor in CB configuration.

[CO2 – L2 - May/June 2012] [10]

CB Configuration:

In common base configuration circuit is shown in figure. Here base is grounded and it is used as the common terminal for both input and output. It is also called as grounded base configuration. Emitter is used as a input terminal where as collector is the output terminal.

#### **Input Characteristics**

It is defined as the characteristic curve drawn between input voltage to input current whereas output voltage is constant.

To determine input characteristics, the collector base voltage  $V_{CB}$  is kept constant

at zero and emitter current  $I_E$  is increased from zero by increasing  $V_{EB}$ .

This is repeated for higher fixed values of V<sub>CB</sub>.

A curve is drawn between emitter current and emitter base voltage at constant collector base voltage is shown in figure.

When  $V_{CB}$  is zero EB junction is forward biased. So it behaves as a diode so that emitter current increases rapidly.

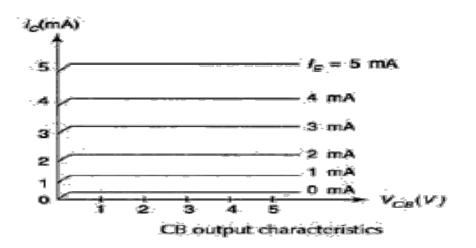

#### **Output Characteristics**

It is defined as the characteristic curve drawn between output voltage to output current whereas input current is constant.

To determine output characteristics, the emitter current  $I_E$  is kept constant at zero and collector current Ic is increased from zero by increasing  $V_{CB}$ .

This is repeated for higher fixed values of IE.

From the characteristic it is seen that for a constant value of IE, Ic is independent of

$V_{CB}$  and the curves are parallel to the axis of  $V_{CB}$ .

As the emitter base junction is forward biased the majority carriers that is electrons from the emitter region are injected into the base region.

In CB configuration a variation of the base-collector voltage results in a variation of the quasi-neutral width in the base. The gradient of the minority-carrier density in the base therefore changes, yielding an increased collector current as the collector-base current is increased. This effect is referred to as the Early effect.

#### Transistor parameters in CB configuration

The slope of CB characteristics will give the following four transistor parameters. It is known as base hybrid parameters.

Input impedance (h<sub>ib</sub>): It is defined as the ratio of change in input voltage (emitter voltage) to change in input current (emitter current) with the output voltage (collector voltage) is kept constant.

$$h_{ib} = \frac{\Delta V_{EB}}{\Delta I_E}$$

,  $V_{CB}$  Constant

This ranges from 20ohms to 50ohms.

II. Output admittance (h<sub>ob</sub>): It is defined as the ratio of change in output current (collector current) to change in output voltage (collector voltage) with the input current (emitter current) is kept constant.

$$h_{ob} = \frac{\Delta I_C}{\Delta V_{CB}}, I_E Constant$$

This ranges from 0.9 to 1.0.

IV. Reverse voltage gain (h<sub>rb</sub>): It is defined as the ratio of change in input voltage (emitter voltage) to change in output voltage (collector voltage) with the input current (emitter current) is kept constant.

$$h_{rb} = \frac{\Delta V_{EB}}{\Delta V_{CB}}, I_E Constant$$

This ranges from  $10^{-5}$  to  $10^{-4}$ .

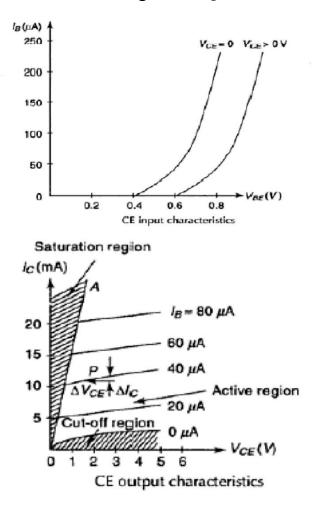

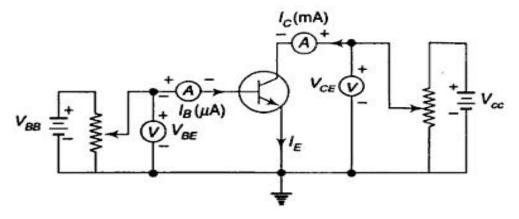

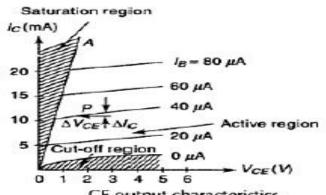

3. Draw the circuit diagram of a NPN transistor CE configuration and the input and output characteristics. Also define its operating regions. [CO2 – L2 - May/June 2015]

[12]

**CE Configuration:**

In common emitter configuration circuit is shown in figure. Here emitter is grounded and it is used as the common terminal for both input and output. It is also called as grounded emitter configuration. Base is used as a input terminal whereas collector is the output terminal.

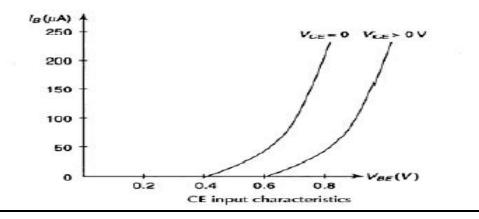

#### Input Characteristics

It is defined as the characteristic curve drawn between input voltage to input current whereas output voltage is constant.

To determine input characteristics, the collector base voltage  $V_{CB}$  is kept constant at zero and base current I<sub>B</sub> is increased from zero by increasing  $V_{BE}$ .

This is repeated for higher fixed values of V<sub>CE</sub>.

A curve is drawn between base current and base emitter voltage at constant collector base voltage is shown in figure.

.Here the base width decreases. So curve moves right as  $\mathsf{V}_{\mathsf{CE}}$  increases.

#### **Output Characteristics**

It is defined as the characteristic curve drawn between output voltage to output current whereas input current is constant.

To determine output characteristics, the base current  $I_B$  is kept constant at zero and collector current Ic is increased from zero by increasing  $V_{CE}$ .

This is repeated for higher fixed values of IB..

From the characteristic it is seen that for a constant value of IB, Ic is independent of

$V_{CB}$  and the curves are parallel to the axis of  $V_{CE}$ .

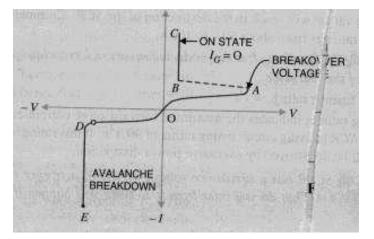

CE output characteristics The output characteristic has 3 basic regions:

- Active region –defined by the biasing arrangements

- Cutoff region region where the collector current is 0A

- Saturation region- region of the characteristics to the left of VCB = 0V

#### Transistor parameters in CE configuration

The slope of CE characteristics will give the following four transistor parameters. It is known as emitter hybrid parameters.

Input impedance (h<sub>ie</sub>): It is defined as the ratio of change in input voltage (base voltage) to change in input current (base current) with the output voltage (collector voltage) is kept constant.

$$h_{ie} = \frac{\Delta V_{EB}}{\Delta I_B}, V_{CE}Constant$$

This ranges from 500ohms to 2000ohms.

II. Output admittance (h<sub>oe</sub>): It is defined as the ratio of change in output current (collector current) to change in output voltage (collector voltage) with the input current (base current) is kept constant.

$$h_{os} = \frac{\Delta I_C}{\Delta V_{CE}}, I_B Constant$$

This ranges from 0.1 to 10µ mhos.

III. Forward current gain (h<sub>fe</sub>): It is defined as the ratio of change in output current (collector current) to change in input current (base current) with the output voltage (collector voltage) is kept constant.

$$h_{fe} = \frac{\Delta I_C}{\Delta I_B}, V_{CE}Constant$$

This ranges from 20 to 200.

IV. Reverse voltage gain (h<sub>re</sub>): It is defined as the ratio of change in input voltage (base voltage) to change in output voltage (collector voltage) with the input current (base current) is kept constant.

$$h_{rs} = \frac{\Delta V_{EB}}{\Delta V_{CE}}, I_B Constant$$

This ranges from  $10^{-5}$  to  $10^{-4}$ .

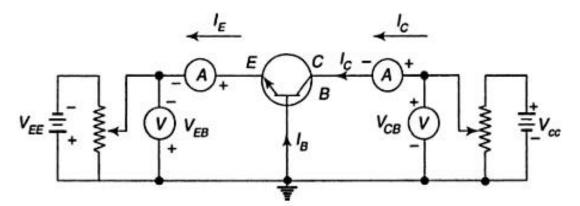

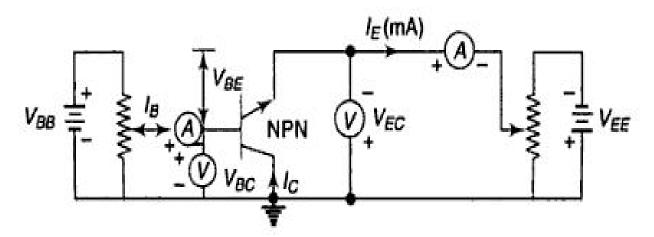

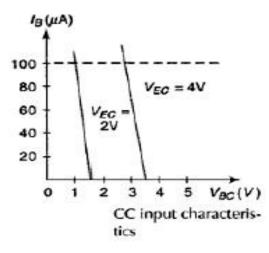

4. Explain the input and output characteristics of a transistor in CC configuration.

[CO2 – L2 - May/June 2013] [10]

CC Configuration:

In common collector configuration circuit is shown in figure. Here collector is grounded and it is used as the common terminal for both input and output. It is also called as grounded collector configuration. Base is used as a input terminal whereas emitter is the output terminal.

#### **Input Characteristics**

II SEM

It is defined as the characteristic curve drawn between input voltage to input current whereas output voltage is constant. To determine input characteristics, the emitter base

voltage  $V_{\mbox{\scriptsize EB}}$  is kept constant at zero and base current  $I_{\mbox{\scriptsize B}}$  is increased from zero by

This is repeated for higher fixed values of  $V_{CE}$ .

A curve is drawn between base current and base emitter voltage at constant collector base voltage is shown in above figure.

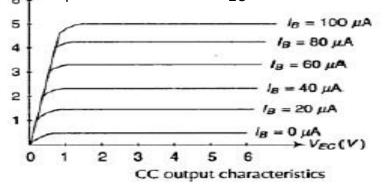

#### **Output Characteristics**

It is defined as the characteristic curve drawn between output voltage to output current whereas input current is constant.

To determine output characteristics, the base current  $I_B$  is kept constant at zero and emitter current  $I_E$  is increased from zero by increasing  $V_{EC}$ .

This is repeated for higher fixed values of IB.

From the characteristic it is seen that for a constant value of  $I_B$ ,  $I_E$  is independent of  $V_{EB}$  and the curves are parallel to the axis of  $V_{EC}$ .

#### Transistor parameters in CC configuration

The slope of CC characteristics will give the following four transistor parameters. It is known as base hybrid parameters.

Input impedance (h<sub>ic</sub>): It is defined as the ratio of change in input voltage (base voltage) to change in input current (base current) with the output voltage (emitter voltage) is kept constant.

$$h_{is} = \frac{\Delta V_{BC}}{\Delta I_B}$$

,  $V_{CE}$  Constant

II. Output admittance (h<sub>oc</sub>): It is defined as the ratio of change in output current (emitter current) to change in output voltage (emitter voltage) with the input current (base current) is kept constant.

$$h_{os} = \frac{\Delta I_E}{\Delta V_{EC}}, I_B Constant$$

III Forward current gain ( $h_{fc}$ ): It is defined as the ratio of change in output current (emitter current) to change in input current (base current) with the output voltage (emitter voltage) is kept constant.

$$h_{fc} = \frac{\Delta I_E}{\Delta I_B}, V_{CE}Constant$$

IV. Reverse voltage gain (h<sub>rc</sub>): It is defined as the ratio of change in input voltage (base voltage) to change in output voltage (emitter voltage) with the input current (base current) is kept constant.

$$h_{rc} = \frac{\Delta V_{BC}}{\Delta V_{EC}}, I_B Constant$$

Electronics and Communication Engineering Department

# 5. Give the comparison of CE, CB, CC configuration. [CO2 – H1 - May/June 2013]

# [6]

A comparison of CB, CE and CC Configurations

| Property          | СВ                  | CE                     | CC                   |

|-------------------|---------------------|------------------------|----------------------|

| Input resistance  | Low (about 100 O)   | Moderate (about 750 Q) | High (about 750 kii) |

| Output resistance | e High (about 450 k | f2) Moderate (about 45 | Low (about 25 O)     |

| kCl)              |                     |                        |                      |

| Current gain      | 1                   | High                   | High                 |

| Voltage gain      | About 150           | About 500              | Less than 1          |

| Phase shift       | 0 or 360°           | 180°                   | 0 or 360°            |

| between input &   |                     |                        |                      |

| output voltages   |                     |                        |                      |

| Applications      | for high frequency  | for audio frequency    | for impedance        |

|                   | circuits            | circuits               | matching             |

# 6. Draw and explain the h-parameter Model for Bipolar Junction Transistor [CO2 -

# L2 - May/June 2015] [8]

#### H-Parameter BJT Model:

The h-parameter model is typically suited to transistor circuit modeling. It is important because:

- 1. its values are used on specification sheets

- 2. it is one model that may be used to analyze circuit behavior

- 3. it may be used to form the basis of a more accurate transistor model

S.K.P. Engineering College, Tiruvannamalai

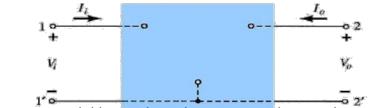

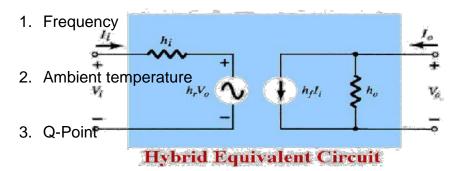

The h parameter model has values that are complex numbers that vary as a function of: Hybrid Equivalent Model

The revised two port network for the h parameter model is shown on the right. At low and mid-band frequencies, the h parameter values are real values. Other models exist because this model is not suited for circuit analysis at high frequencies The h-parameter model is defined by:

$$V_1 = h_{11}I_1 + h_{12}V_2(\text{KVL})$$

$$I_2 = h_{21}I_1 + h_{22}V_2(\text{KCL})$$

Electronics and Communication Engineering Department

The h-parameter model for the common emitter circuit is on the fig. On spec sheet:

$$h_{11} = h_{ix}$$

$$h_{12} = h_{rx}$$

$$h_{21} = h_{fx}$$

$$h_{22} = h_{ox}$$

# . Explain briefly about the Gummel Poon model [CO2 – L2 - Nov/Dec 2015]

[10]

#### • Gummel-Poon Model:

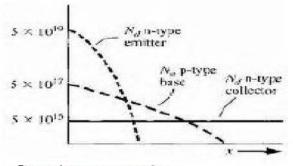

The Gummel-Poon model of the BIT considers more physics of the transistor that the Ebers-Moll model. This model can he used if, for example, there is a non-uniform doping concentration in the base.

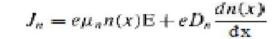

The electron current density in the base of m npn transistor can be written as

An electric field will occur in the base if non uniform doping exists in the base. Electric field can be written as

$$E = \frac{KT}{e} \cdot \frac{l}{P(x)} \cdot \frac{dp(x)}{dx}$$

where p(x) is the majority carrier hole concentration in the base. Under low injection, the hole concentration is just the acceptor impurity concentration. With the doping profile shown in Figure. The electric field is negative (from the collector to the emitter). The direction of this electric field aids the flow of electrons across the base.

Substituting previous Equation we get

$$J_n = e\mu_n n(x) \cdot \frac{KT}{e} \cdot \frac{l}{P(x)} \cdot \frac{dp(x)}{dx} + eD_n \frac{dn(x)}{dx}$$

Using Einstein's relation, we can write Equation in the form

$$J_n = \frac{eD_n}{P(x)} \left[ n(x)\frac{dP(x)}{dx} + P(x)\frac{dn(x)}{dx} \right] - \frac{eD_n}{P(x)}\frac{dP(n)}{dx}$$

Impurity concentration profiles of a double-diffused npn bipolar transistor.

It is written in the form of

$$\frac{I_n P(x)}{eD_n} = \frac{d(Pn)}{dx}$$

Integrating this eqn through the base

$$\frac{J_n}{eD_n} \int_0^x \int_0^x P(x) dx - \int_0^x \frac{dP(x)}{dx} dx - P(x_B)n(x_B) - P(0)n(0)$$

The integral in the denominator is the total majority carrier charge in the base and is known as the base Gummel number; defined as Q<sub>B</sub>.

The hole current density in the emitter of an NPN transistor can be expressed as,

$$J_p = \frac{-eD_p n_i^2 \exp\left(\frac{V_{BE}}{Vt}\right)}{\int_0^{xB} n(x)^2 dx^2}$$

Electronics and Communication Engineering Department

With the doping profile shown in Figure. The electric field is negative (from the collector to the emitter). The direction of this electric field aids the flow of electrons across the base.

The integral in the denominator is the total majority carrier charge in the emitter and is known as the emitter Gummel number, defined as Q<sub>E</sub>.

The Gummel-Poon model can also take into account non ideal effects, such as the Early effect and high-level injection.

If the B-E voltage becomes too large. low injection no longer applies, which leads to high-level injection. In this case, the total hole concentration in the base increases because of the increased excess hole concentration. This means that the base Gummel number will increase.

The Gummel-Poon model can then he used to describe the basic operation of the transistor as well as to describe non ideal effects.

8. How multi emitter transistor is working? Explain it with neat diagram. [CO2 – L2

May/June 2015] [12

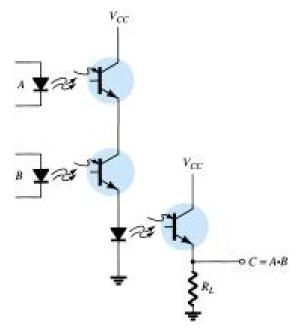

Multi Emitter Transistor (Transistor Transistor Logic):

TTL inputs are the emitters of a multiple-emitter transistor. This IC structure is functionally equivalent to multiple transistors where the bases and collectors are tied together. The output is buffered by a common emitter amplifier.

**Inputs both logical ones.** When all the inputs are held at high voltage, the baseemitter junctions of the multiple-emitter transistor are reverse-biased. Unlike DTL, a small —collectorll current (approximately 10µA) is drawn by each of the inputs. This is because the transistor is in reverse-active mode.

An approximately constant current flows from the positive rail, through the resistor and into the base of the multiple emitter transistor. This current passes through the base-emitter junction of the output transistor, allowing it to conduct and pulling the output voltage low (logical zero).

An input logical zero. Note that the base-collector junction of the multiple-emitter transistor and the base-emitter junction of the output transistor are in series between the bottom of the resistor and ground. If one input voltage becomes zero, the corresponding base-emitter junction of the multiple-emitter transistor is in parallel with these two junctions. A phenomenon called current steering means that when two voltage-stable elements with different threshold voltages are connected in parallel, the current flows through the path with the smaller threshold voltage. As a result, no current flows through the base of the output transistor, causing it to stop conducting and the output voltage becomes high (logical one). During the transition the input transistor is briefly in its active region; so it draws a large current away from the base of the output transistor and thus quickly discharges its base. This is a critical advantage of TTL over DTL that speeds up the transition over a diode input structure.

The main disadvantage of TTL with a simple output stage is the relatively high output resistance at output logical "1" that is completely determined by the output collector resistor. It limits the number of inputs that can be connected (the fanout). Some

advantage of the simple output stage is the high voltage level (up to  $V_{CC}$ ) of the output logical "1" when the output is not loaded.

# 9. Explain details about the Ebers Moll model. [CO2 – L2 - May/June 2013]

# [12]

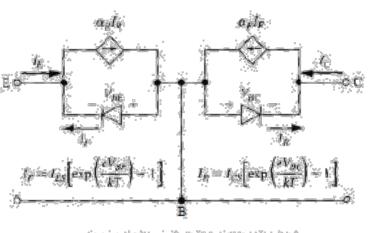

# Ebers-Moll Model:

The Ebers-Moll model, or equivalent circuit, is one of the classic models of the bipolar transistor. This particular model is based on the interacting diode junctions and applicable in any of the transistor operating modes. Figure shows the current directions and voltage polarities used in the Ebers Moll model. The currents are defined as all entering the terminals so that

$$I_{E} + I_{B} + I_{C} = 0$$

The direction of the emitter current is opposite to what we have considered up to point, but as long as we are consistent in the analysis, the defined direction does not matter. The collector current can be written in general as

$$lc = \alpha_F I_F - I_R$$

where  $\alpha_F$  is the common base current rain in the forward-active mode. In this mode.

$$lc = \alpha_F I_F + I_{CS}$$

where the current Ics is the reverse-bias B-C junction current. The current is given by

$$I_F = I_{ES}\left[exp^{\left(\frac{eV_E}{KT}\right)} - 1\right]$$

If the B-C junction becomes forward biased, such as in saturation, then we can write the current *IR* as

$$I_{R} = I_{CS} \left[ exp^{\left( \frac{eV_{BC}}{RT} \right)} - 1 \right]$$

Electronics and Communication Engineering Department

Using above equations collector current written as

Basic Ebers-Mollequivalent cucuit.

$$\begin{split} I_E &= \alpha_R I_R - I_F \\ I_E &= \alpha_R I_{CS} \left[ \exp \left( \frac{e V_{BC}}{KT} \right) - 1 \right] - I_{ES} \left[ \exp \left( \frac{e V_{BE}}{KT} \right) - 1 \right] \end{split}$$

53

The current IEs is the reverse-bias B-E junction current and u~ is the common base current gain for the inverse-active mode. The current sources in the equivalent circuit represent current components that depend on voltages across other junctions. The Ebers-Moll model has four parameters:  $\alpha_F$ ,  $\alpha_R$ ,  $I_{ES}$  and Ics. However, only three parameters are independent. The reciprocity relationship states that

Normally in electronic circuit applications, the collector-emitter voltage at saturation is of interest. We can define the C-E saturation voltage as Combining the previous some eqn we get

Current direction and voltage polarity definitions for the Ebers-Moll model.

$$I_{E} = \alpha_{R} I_{CS} \left[ \exp\left(\frac{eV_{BC}}{KT}\right) - 1 \right] - I_{ES} \left[ \exp\left(\frac{eV_{BE}}{KT}\right) - 1 \right]$$

If we solve for the value of and sub in previous one and simplifying we get

$$I_{E} = \alpha_{R} I_{CS} \left[ \exp\left(\frac{eV_{BC}}{KT}\right) - 1 \right] - I_{ES} \left[ \exp\left(\frac{eV_{BE}}{KT}\right) - 1 \right]$$

The ratio of Ics to I<sub>E</sub>s can be written in terms of  $\alpha_F$  and  $\alpha_R$  and we finally get

$V_{BE} = V_T l_n [I_C (1 - \alpha_R) + I_B + I_{ES} (1 - \alpha_F C_R) / I_{ES} (1 - \alpha_F \alpha_R)]$

$$V_{CE}(sat) = V_{T}l_{n}\left[\frac{I_{C}(1-\alpha_{R})+I_{B}}{\alpha_{F}I_{B}-(1-\alpha_{F})I_{C}},\frac{\alpha_{F}}{\alpha_{R}}\right]$$

Electronics and Communication Engineering Department

#### <u>Unit - III</u>

#### Field Effect Transistors

#### Part - A

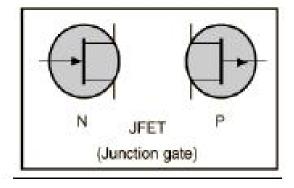

#### 1. Why it is called field effect transistor? [CO3 – L2 - May/June 2013]

The drain current  $I_D$  of the transistor is controlled by the electric field that extends into the channel due to reverse biased voltage applied to the gate, hence this device has been given the name Field Effect Transistor.

#### 2. Why FET is called voltage controlled device. [CO3 – L2 - May/June 2014]

*FET* the value of the current depends upon the value of the voltage applied at the ate and drain. So it is *known as voltage controlled device*.

#### 3. Define the term threshold voltage. [CO3 – L2 - Nov/Dec 2013]

The threshold voltage, commonly abbreviated as  $V_{th}$ , of a field-effect transistor (FET) is the value of the gate-source voltage when the conducting channel just begins to connect the source and drain contacts of the transistor, allowing significant current. The threshold voltage of a junction field-effect transistor is often called **pinch-off** voltage instead, which is somewhat confusing since "pinch off" for an insulated-gate field-effect transistor is used to refer to the channel pinching that leads to current saturation behavior under high source-drain bias, even though the current is never off. The term "threshold voltage" is unambiguous and refers to the same concept in any field-effect transistor.

#### 4. What is channel length modulation? [CO3 – L2 - May/June 2014]

One of several short-channel effects in MOSFET scaling, **channel length modulation** (**CLM**) is a shortening of the length of the inverted channel region with increase in drain bias for large drain biases.

As the drain voltage increases, its control over the current extends further toward the source, so the un inverted region expands toward the source, shortening the length of the channel region, the effect called *channel-length modulation*.

# 5. Compare JFET with BJT. [CO3 – L2 - May/June 2015]

- FET operation depends only on the flow of majority carriers-holes for P-channel FETs and electrons for N-channel FETs. Therefore, they arc called Unipolar devices. Bipolar transistor (BJT) operation depends on both minority and majority current carriers.

- As FET has no junctions and the conduction is through an N-type or P-type semiconductor material. FET is less noisy than BJT.

- As the input circuit of FET is reverse biased, FET exhibits a much higher input impedance (in the order of 100 M) and lower output impedance and there will be a high degree of isolation between input and output. So. FET can act as an excellent buffer amplifier but the BJT has low input impedance because its input circuit is forward biased.

- FET is a voltage controlled device, i.e. voltage at the input terminal controls the output current, whereas BJT is a current controlled device, i.e. the input current controls the output current.

- FETs are much easier to fabricate and are particularly suitable for ICs because they occupy less space than BJTs.

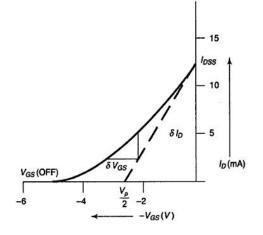

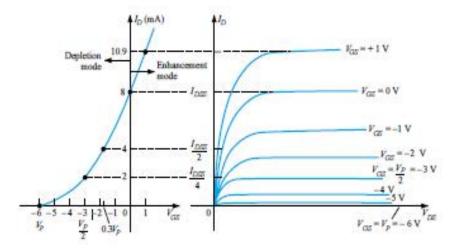

- 6. Draw the transfer characteristics curve for JFET. [CO3 L2 May/June 2015]

# 7. Differentiate between N and P channel FETs [CO3 – L2 - Nov/Dec 2014]

- 1. In an N channel JFET the current carriers are electrons, whereas the current carriers are holes in a P channel JFET.

- Mobility of electrons is large in N channel JFET; Mobility of holes is poor in P channel JFET.

- 3. The input noise is less in N channel JFET than that of P channel JFET.

- 4. The transconductance is larger in N channel JFET than that of P channel JFET.

- 8. Write some applications for JFET. [CO3 L3 May/June 2013]

- 1. FET is used as a buffer in measuring instruments, receivers since it has high input impedance and low output impedance.

- 2. FETs arc used in RF amplifiers in FM tuners and communication equipment for the low noise level.

- 3. Since the input capacitance is low. FETs are used in cascade amplifiers in measuring and test equipments.

- 4. Since the device is voltage controlled, it is used as a voltage variable resistor in operational amplifiers and tone controls.

- 5. FETs are used in mixer circuits in FM and TV receivers, and communication equipment because inter modulation distortion is low.

#### 9. Compare MOSFET with JFET. [CO3 – L2 - May/June 2015]

- In enhancement and depletion types of MOSFET. the transverse lectric field induced across an insulating layer deposited on the semiconductor material controls the conductivity of the channel. In the JFET the transverse electric field across the reverse biased PN junction controls the conductivity of the channel.

- The gate leakage current in a MOSFET is of the order of 10<sup>12</sup>

A. Hence the input resistance of a MOSFET is very high in the order of 10<sup>10</sup> to 10<sup>W</sup> *i1.* The gate leakage current of a JFET is of the order of 10<sup>"9</sup> A and its input resistance is of the order of 10\* ft.

- The output characteristic\* of the JFET are flatter than those of the MOSFET and hence, the drain resistance of a JFET (0.1 to I) is much higher than that of a MOSFET (I to 50).

- JFETs arc operated only in the depletion mode. The depletion type MOSFET may be operated in both depletion and enhancement mode.

•

Comparing to JFET. MOSFETs are easier to fabricate.

# 10. Compare N channel MOSFET with P channel MOSFET. [CO3 – L2 - May/June 2014]

- The P-channel enhancement MOSFET is very popular because it is much easier and cheaper to produce than the N-channel device.

- The hole mobility is nearly 2.5 times lower than the electron mobility. Thus, a P-channel MOSFET occupies a larger area than an N-channel MOSFET having the same  $I_n$  rating.

- The drain resistance of P-channel MOSFET is three times higher than that for an identical N-channel MOSFET.

- The N-channel MOSFET has the higher packing density which makes it faster in switching applications due to the smaller junction areas and lower inherent capacitances.

- The N-channel MOSFET is smaller for the same complexity than Pchannel device.

11. Differentiate between current voltage relationships of the N channel and P channel MOSFET [CO3 – L2 – Nov/Dec2013]

| N-Oumnel MOSFET                              | P-Channel MOSFET                         |  |

|----------------------------------------------|------------------------------------------|--|

| Saturation region $\{V_{NS} > V_{D5}(sat)\}$ | Saturation region $[V_{sn} > Vy, (sat))$ |  |

| Non saturation region (V^j < V^saO)              | Non saturation region (V <sup><math>\wedge</math></sup> < V <sup><math>\wedge</math></sup> sat)) t <sub>D</sub> = |  |

|--------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|--|

| $/z \ge 12(V_{cs}-V_{M})V_{M}-s_{s}$             | $(Vs_{C}+V_{TP})V_{SD}-VI_{s}]$                                                                                   |  |

| Transition point V <i>,,,(sa</i> >I = I',, - V,, | Transition point <i>IfafM-Ib&lt;</i> » V,,                                                                        |  |

| Enhancement mode V,,>0                           | Enhancement mode W, < 0                                                                                           |  |

| Depletion mode $Vt \approx 0$                    | Depiction mode $V_7$ , > ( »                                                                                      |  |

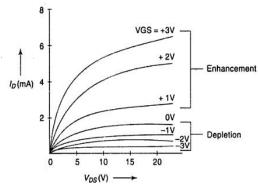

#### 12. Draw the V-I characteristics curve of MOSFET. [CO3 – L2 - May/June 2013]

PART B

1. Explain the operation of JFET and derive the drain and transfer characteristics.

[CO3 – L2 - May/June 2014]

[16]

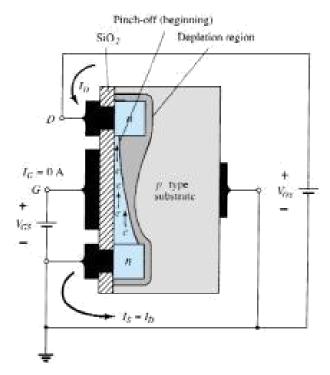

Junction FETs (JFETs)

Electronics and Communication Engineering Department

JFETs consists of a piece of high-resistivity semiconductor material (usually Si) which constitutes a channel for the majority carrier flow.Conducting semiconductor channel between two ohmic contacts – source & drain.JFET is a high-input resistance device, while the BJT is comparatively low.

If the channel is doped with a donor impurity, n-type material is formed and the channel current will consist of electrons.

If the channel is doped with an acceptor impurity, p-type material will be formed and the channel current will consist of holes.

N-channel devices have greater conductivity than p-channel types, since electrons have higher mobility than do holes; thus n-channel JFETs are approximately twice as efficient conductors compared to their p-channel counterparts.

The magnitude of this current is controlled by a voltage applied to a gate, which is a reverse-biased.

The fundamental difference between JFET and BJT devices: when the JFET junction is reverse-biased the gate current is practically zero, whereas the base current of the BJT is always some value greater than zero.

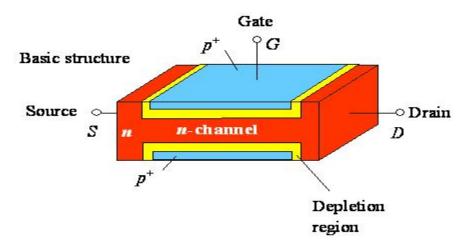

#### **Basic structure of JFETs**

- In addition to the channel, a JFET contains two ohmic contacts: the source and the drain.

- The JFET will conduct current equally well in either direction and the source and drain leads are usually interchangeable. N-channel JFET

- This transistor is made by forming a channel of N-type material in a P-type substrate.

- Three wires are then connected to the device.

- One at each end of the channel.

- One connected to the substrate.

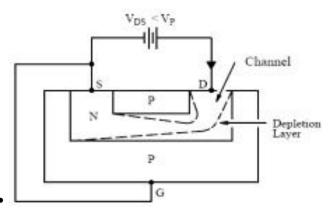

In a sense, the device is a bit like a PN-junction diode, except that there are two wires connected to the N-type sideThe gate is connected to the source.

• Since the pn junction is reverse-biased, little current will flow in the gate connection.

• The potential gradient established will form a depletion layer, where almost all the electrons present in the n-type channel will be swept away. The most depleted portion is in the high field between the G and the D, and the least-depleted area is between the G

and the S.

• Because the flow of current along the channel from the (+ve) drain to the (-ve) source is really a flow of free electrons from S to D in the n-type Si, the magnitude of this current will fall as more Si becomes depleted of free electrons.

• There is a limit to the drain current (ID) which increased VDS can drive through the channel.

• This limiting current is known as IDSS (*Drain-to-Source current with the gate shorted to the source*).

- The output characteristics of an n-channel JFET with the gate short-circuited to the source.

- The initial rise in ID is related to the buildup of the depletion layer as VDS increases.

- The curve approaches the level of the limiting current IDSS when ID begins to be pinched off.

- The physical meaning of this term leads to one definition of pinch-off voltage, VP , which is the value of VDS at which the maximum IDSS flows.

- With a steady gate-source voltage of 1 V there is always 1 V across the wall of the channel at the source end.

- A drain-source voltage of 1 V means that there will be 2 V across the wall at the drain end.

(The drain is \_up' 1V from the source potential and the gate is 1V \_down', hence the total difference is 2V.)

• The higher voltage difference at the drain end means that the electron channel is squeezed down a bit more at this end.

• When the drain-source voltage is increased to 10V the voltage across the channel walls at the drain end increases to 11V, but remains just 1V at the source end.

• The field across the walls near the drain end is now a lot larger than at the source end.

• As a result the channel near the drain is squeezed down quite a lot.

• Increasing the source-drain voltage to 20V squeezes down this end of the channel still

more.As we increase this voltage we increase the electric field which drives electrons along the open part of the channel. However, also squeezes down the channel near the drain end. This reduction in the open channel width makes it harder for electrons to pass.

• As a result the drain-source current tends to remain constant when we increase the drain source voltage.

- Increasing V<sub>DS</sub> increases the widths of depletion layers, which penetrate more into channel and hence result in more channel narrowing toward the drain.

- The resistance of the n-channel, RAB therefore increases with VDS.

- The drain current: IDS = VDS/RAB

- ID versus VDS exhibits a sub linear behavior, see figure for VDS < 5V.

• The pinch-off voltage, V<sub>P</sub> is the magnitude of reverse bias needed across the p+n junction to make them just touch at the drain end.

• Since actual bias voltage across  $p_+n$  junction at drain end is V<sub>GD</sub>, the pinch-off occur whenever: V<sub>GD</sub> = -V<sub>P</sub>.

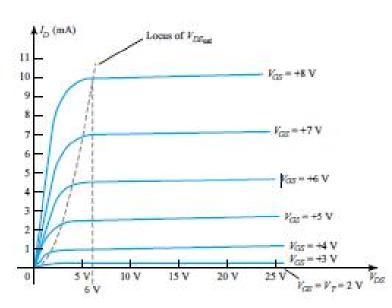

#### **JFET: I-V characteristics**

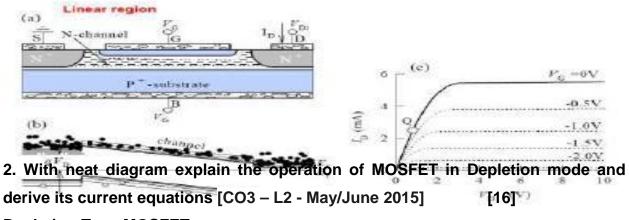

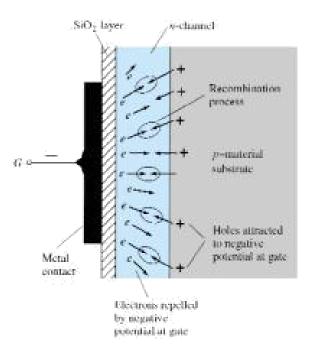

#### **Depletion-Type MOSFET**

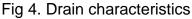

MOSFETs are further broken down into depletion type and enhancement type. The terms depletion and enhancement define their basic mode of operation, while the label MOSFET stands for metal-oxide-semiconductor-field-effect transistor.

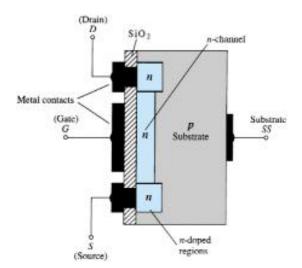

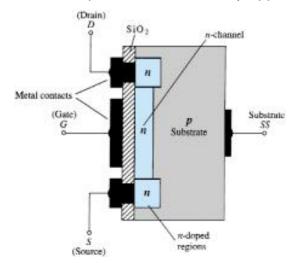

#### **Basic Construction**

The basic construction of the n-channel depletion-type MOSFET is provided in Fig. A

slab of p-type material is formed from a silicon base and is referred to as the substrate. It is the foundation upon which the device will be constructed. In some cases the substrate is internally connected to the source terminal. However, many discrete devices provide an additional terminal labeled SS, resulting in a four-terminal device, such as that appearing in Fig. 1

The source and drain terminals are connected through metallic contacts to ndoped regions linked by an n-channel as shown in the figure. The gate is also connected to a metal contact surface but remains insulated from the n-channel by a very thin silicon dioxide (SiO<sub>2</sub>) layer. SiO<sub>2</sub> is a particular type of insulator referred to as a dielectric that sets up opposing (as revealed by the prefix di-) electric fields within the dielectric when exposed to an externally applied field.

There is no direct electrical connection between the gate terminal and the channel of a MOSFET.

It is the insulating layer of SiO2 in the MOSFET construction that accounts for the very desirable high input impedance of the device.

#### **Basic Operation and Characteristics**

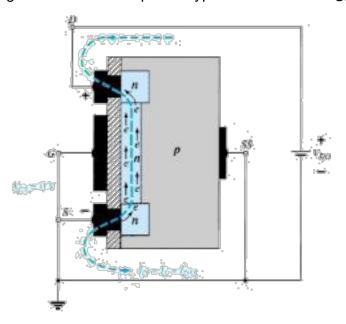

In Fig. 2 the gate-to-source voltage is set to zero volts by the direct connection from one terminal to the other, and a voltage VDS is applied across the drain-to-source terminals. The result is an attraction for the positive potential at the drain by the free electrons of the n-channel and a current similar to that established through the channel of the JFET. In fact, the resulting current with  $V_{GS} = 0$  V continues to be labeled IDSS, as shown in Fig. 3.Fig 2. n – channel depletion type MOSFET with  $V_{GS} = 0$  V

Electronics and Communication Engineering Department

Fig.4 Reduction in free carriers in channel due to -ve potential

In Fig. 4, VGS has been set at a negative voltage such as -1 V. The negative potential at the gate will tend to pressure electrons toward the p-type substrate (like charges repel) and attract holes from the p-type substrate (opposite charges attract) as shown in Fig. 4. Depending on the magnitude of the negative bias established by  $V_{GS}$ , a level of recombination between electrons and holes will occur that will reduce the number of free electrons in the n-channel available for conduction. The more negative the bias, the higher the rate of recombination.

For positive values of  $V_{GS}$ , the positive gate will draw additional electrons (free carriers) from the p-type substrate due to the reverse leakage current and establish new carriers through the collisions resulting between accelerating particles. As the gate-to-source voltage continues to increase in the positive direction, Fig. 3 reveals that the drain current will increase at a rapid rate.

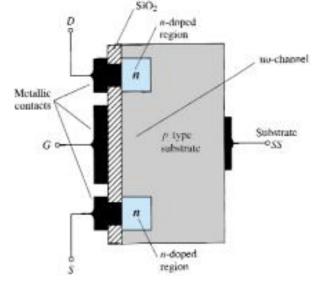

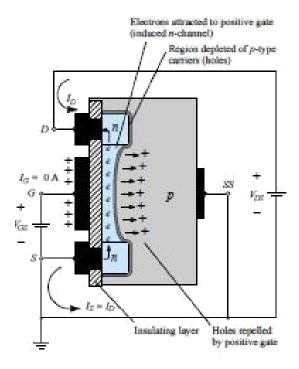

# 3. With neat diagram explain the operation of MOSFET in Enhancement mode and derive its current equations [CO3 –H1 - Nov/Dec 2013] [16] Enhancement-Type MOSFET:

#### **Basic Construction**

The basic construction of the n-channel enhancement-type MOSFET is provided in Fig.1. A slab of p-type material is formed from a silicon base and is again referred to as the substrate. As with the depletion-type MOSFET, the substrate is sometimes internally connected to the source terminal, while in other cases a fourth lead is made available for external control of its potential level.

The SiO<sub>2</sub> layer is still present to isolate the gate metallic platform from the region between the drain and source, but now it is simply separated from a section of the p-type material. In summary, therefore, the construction of an enhancement-type

MOSFET is quite similar to that of the depletion-type MOSFET, except for the absence of a channel between the drain and source terminals.

Fig 1. N channel enhancement type MOSFET

**Basic Operation and Characteristics**

If  $V_{GS}$  is set at 0 V and a voltage applied between the drain and source of the device of Fig. 1, the absence of an n-channel (with its generous number of free carriers) will result in a current of effectively zero amperes—quite different from the depletion- type MOSFET and JFET where  $I_D - I_{DSS}$ . It is not sufficient to have a large accumulation of carriers (electrons) at the drain and source (due to the n-doped regions) if a path fails to exist between the two. With VDS some positive voltage, VGS at 0 V, and terminal SS directly connected to the source, there are in fact two reverse-biased p-n junctions between the n-doped regions and the p-substrate to oppose any significant flow between drain and source.

In Fig. 2 both VDS and VGS have been set at some positive voltage greater than 0 V, establishing the drain and gate at a positive potential with respect to the source. The positive potential at the gate will pressure the holes (since like charges repel) in the p-substrate along the edge of the SiO2 layer to leave the area and enter deeper regions of the p-substrate, as shown in the figure.

Fig 2. Channel formation

As VGS is increased beyond the threshold level, the density of free carriers in the induced channel will increase, resulting in an increased level of drain current. However, if we hold VGS constant and increase the level of VDS, the drain current will eventually reach a saturation level as occurred for the JFET and depletion-type MOSFET. The leveling off of  $I_D$  is due to a pinching-off process depicted by the narrower channel at the drain end of the induced channel as shown in Fig. 3. Applying Kirchhoff's voltage law to the terminal voltages of the MOSFET of Fig. 3, we find that

$$V_{DG} = V_{DS} - V_{GS}$$

The drain characteristics of Fig. 5.34 reveal that for the device of Fig 3 with VGS = 8 V, saturation occurred at a level of VDS = 6 V. In fact, the saturation level for VDS is related to the level of applied VGS by

V<sub>DSsat</sub> = V<sub>GS</sub> - V<sub>T</sub>

For levels of VGS > VT, the drain current is related to the applied gate-to-source voltage by the

following nonlinear relationship:

$$I_{\rm D} = k(V_{\rm GS} - V_{\rm T})^2$$

Again, it is the squared term that results in the nonlinear (curved) relationship between ID and VGS. The k term is a constant that is a function of the construction of the device. The value of k can be determined from the following equation where ID(on) and VGS(on) are the values for each at a particular point on the characteristics of the device.

# **4. Give some characteristics of MOSFET. [CO3 – L2 - Nov/Dec 2014] [8]** MOSFET I-V CHARACTERISTICS

1.

ook up the circuit of Fig. 2. This circuit will be used in the following steps to investigate the i-v characteristics of the n-channel MOSFET. The chip used in this experiment is a CD4007, containing six MOSFETs. We will use only one of them, as shown in the pin assignment in Fig. 3. Figure 3 2.

- Set vGS = 5 V Measure the drain current iDS, versus the drain-source voltage, vDS, from 0 to 5 V Make sure you take measurements at a sufficient number of vDS values since you will later need to plot iDS versus vDS. Include a point at vDS = 0.1 V for later use.

- 3. 3. Repeat the entire step 2 for vGS = 3 V and vDS = 1 V. 1 It should be noted that the only DC current in the device is the drain-to-source current iDS. The gate is internally separated by an insulator from the channel, so the gate current is practically zero.

- 4. 4. With vDS = 5 V, determine the value of vGS at which the current iDS becomes negligible; assume that for our purposes this means 5mA. This value of vGS is close to the so-called threshold voltage of the transistor, and it is positive for an "enhancement mode" MOSFET, which is what we are working with here.2

- 5. 5. Using the data you have collected in steps 2 and 3, plot a family of curves for the drain current, iDS, versus the drain-source voltage, vDS from 0 to 5 V, with vGS as a parameter. Use a single set of vDS iDS axes for this plot. There should be one curve for each vGS value (1 V, 3 V, and 5 V) on this family of curves. Label each curve with the corresponding vGS value.

- 6.

6. You should be able to observe on the above plot that, for each curve, the current tends to a constant (or, as we say, saturates) as

74

н

vDS is made large. What is, approximately, the saturation value of the current for each of the three vGS values.

# 5. Explain the operation of dual gate MOSFET [CO3 – L2 - Nov/Dec 2015] [8]

One form of MOSFET that is particularly popular in many RF applications is the dual gate MOSFET. The dual gate MOSFET is used in many RF and other applications where two control gates are required in series.

The dual gate MOSFET is essentially a form of MOSFET where two gates are fabricated along the length of the channel - one after the other. In this way, both gates affect the level of current flowing between the source and drain.

In effect, the dual gate MOSFET operation can be considered the same as two MOSFET devices in series. Both gates affect the overall MOSFET operation and hence the output. In effect, the dual gate MOSFET operation can be considered the same as two MOSFET devices in series. Both gates affect the overall MOSFET operation and hence the output.

# Dual gate MOSFET circuit symbol

The dual gate MOSFET can be used in a number of applications including RF mixers /multipliers, RF amplifiers, amplifiers with gain control and the like.

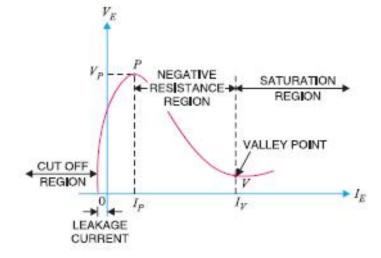

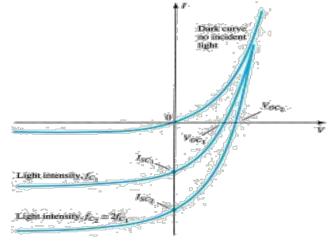

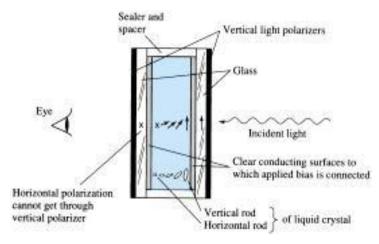

Dual gate MOSFET structure